Nanowire transistors

DOI: 10.1002/smll.200600379

## High Electron Mobility InAs Nanowire Field-Effect **Transistors**

Shadi A. Dayeh, David P. R. Aplin, Xiaotian Zhou, Paul K. L. Yu, Edward T. Yu,\* and Deli Wang\*

**S**ingle-crystal InAs nanowires (NWs) are synthesized using metal organic chemical vapor deposition (MOCVD) and fabricated into NW field-effect transistors (NWFETs) on a SiO $\sqrt{n^+}$ -Si substrate with a global  $n^+$ -Si back-gate and sputtered SiO<sub>x</sub>/Au underlap top-gate. For top-gate NWFETs, we have developed a model that allows accurate estimation of characteristic NW parameters, including carrier field-effect mobility and carrier concentration by taking into account series and leakage resistances, interface state capacitance, and top-gate geometry. Both the back-gate and the top-gate NWFETs exhibit room-temperature field-effect mobility as high as  $6580 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , which is the lower-bound value without interface-capacitance correction, and is the highest mobility reported to date in any semiconductor NW.

## Keywords:

- · electron mobility

- · field-effect transistors

- nanoelectronics

- · nanowires

#### 1. Introduction

Semiconductor nanowires are very attractive and versatile building blocks for future electronic systems because of the unique possibilities they offer for the rational control of fundamental properties such as dimension, composition, and doping during growth.<sup>[1,2]</sup> A wide range of nanowire (NW)based devices and systems, including transistors and circuits, [3-5] light emitters, [6-9] and sensors, [10] have been explored. Nanowire field-effect transistors (NWFETs) have been of particular interest recently, both as vehicles for the investigation of basic carrier-transport behavior and as pofuture high-performance electronic devices. NWFETs fabricated from group  $IV_{,}^{[11-13]}$   $III-V_{,}^{[3,14-16]}$  and II-VI<sup>[17,18]</sup> semiconductors and conductive oxides<sup>[19]</sup> have demonstrated promising FET characteristics in topgate, [11,12,15] back-gate, [3,14,15] and surround-gate [16,18] FET geometries. InAs in particular is an attractive candidate for NW-based electronic devices because of its very high electron mobility at room temperature<sup>[20]</sup> and its surface Fermilevel pinning in the conduction band, [21] which lead to the formation of an electron surface accumulation layer[22] and allow straightforward formation of low-resistance ohmic contacts.<sup>[23]</sup> Indeed, resonant tunneling diodes,<sup>[24]</sup> single-electron transistors, [25] and Josephson junctions [26] have been implemented using InAs NWs and InAs/InP NW heterostructures with carrier mobilities in the range of 200-3000  $cm^2V^{-1}s^{-1}$ .[16,25]

Herein, we report room-temperature studies of depletion-mode InAs-based NWFETs with both global back-gate and underlap (i.e. nonzero spacing to source/drain electrodes) top-gate geometries. We also present a circuit model for top-gate FETs that takes into account the contact, series and leakage resistances, interface-state capacitance, and topgate geometry-defined capacitance to assure accurate parameter extraction for such structures from device measurements. We have analyzed the InAs NWFETs using this new model and the conventional back-gate NWFET model. In

Fax: (+1) 858-534-0556 E-mail: ety@ece.ucsd.edu dwang@ece.ucsd.edu

Supporting information for this article is available on the WWW under http://www.small-journal.com or from the author.

<sup>[\*]</sup> S. A. Dayeh, D. P. R. Aplin, X. Zhou, Prof. P. K. L. Yu, Prof. E. T. Yu, Prof. D. Wang Department of Electrical and Computer Engineering University of California San Diego (UCSD), 9500 Gilman Drive, Mail Code 0407 La Jolla, CA 92093-0407 (USA)

small ...

both cases, we obtained field-effect electron mobility values significantly higher than those reported to date for other semiconductor NWs.

### 2. Results and Discussion

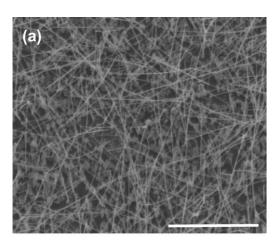

The as-grown InAs nanowires on a  $SiO_2/n^+$ -Si substrate were 30–75 nm in diameter and 20–30  $\mu$ m long, as shown in the representative scanning electron microscopy (SEM) image (Figure 1a). The InAs NWs were single-crystal Wurzite with the growth axis in the [110] direction, as shown in the high-resolution transmission electron microscopy (HRTEM) image (Figure 1b).

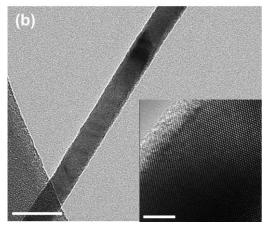

The InAs NWFET devices were then fabricated using electron-beam lithography (EBL) with Ti/Al source and drain electrodes and a SiO<sub>x</sub>/Au top-gate electrode. The n<sup>+</sup>-Si substrate served as a global back gate. Figure 2 a shows the schematic of an underlap top-gate NWFET device. Careful consideration of the device geometry of this structure suggests the need for an analysis that extends beyond those employed previously<sup>[3,12–14,16,18]</sup> in order to extract key characteristic nanowire parameters, such as mobili-

Figure 1. a) SEM image of InAs nanowires on a  $SiO_2$  substrate. Scale bar is 20  $\mu$ m. b) TEM image of an InAs nanowire. Scale bar is 50 nm. The inset is a HRTEM image of the same single-crystal InAs nanowire. Scale bar is 5 nm.

ty and carrier concentration. Specifically, we have taken into account the contact resistance, the resistance of the ungated NW regions between the source/drain and gate electrodes, and the unmodulated NW volume underneath the gate, which are important factors that have not been accounted for in prior reported studies. Because the Fermi level is pinned in the conduction band at the InAs surface, the ungated portions of the NW remain conducting with no band bending under top-gate bias, as illustrated in Figure 2b; the resistance of each NW section should therefore be calculated separately to analyze device current-voltage characteristics. We thus define two series resistances  $R_{\rm s1}$  and  $R_{\rm s2}$ , each of which includes the contact resistance and the resistance of the corresponding ungated NW segments. The unmodulated portion of the nanowire underneath the gate gives rise to a current-leakage path that is constant for a wide range of negative gate voltages and can be described by a leakage resistance,  $R_{leak}$ , which can be obtained from the lowest measured current in the device,  $I_{leak}$ . The gateleakage current through the thick oxide is negligible so that the gate-leakage resistance is not included in this model. Figure 2c shows the resulting equivalent circuit model employed in our analysis;  $V_{DS}^{0}$  and  $V_{GS}^{0}$  are the applied sourcedrain and gate-source voltages, respectively, and  $I_{DS}^0$  is the measured source-drain current.  $V_{DS}$ ,  $V_{GS}$  and  $I_{DS}$  are related to the active transistor portion of the device.

The resistances of the InAs NWs were measured from devices fabricated with source-drain separations that varied from 0.5 to 4 µm in the same processing run, and without a top gate, the extrapolation to a source-drain separation of zero yielded an ohmic contact resistance in the range of  $1-10 \text{ k}\Omega$  (see Supporting Information). As a conservative estimate in the computation of the mobility, a contact resistance of  $1 k\Omega$  has been used; this assumes the highest possible NW-resistance values. Numerical calculation to determine the number of confined modes in the InAs nanowires by solving Schrödinger's equation in cylindrical coordinates<sup>[27]</sup> yields the occupation of 10 modes for the carrier densities calculated in these wires (as discussed later), which in turn results in a contact resistance of  $1.3 \text{ k}\Omega$  due to the mismatch in the one-dimensional (1D, NW) and 3D (metal contact) density of states.<sup>[28]</sup> This result suggests, as expected, the absence of a significant Schottky barrier at the Al-Ti/InAs interface.

In the linear operating region, [19] the accumulation charge is given by  $Q_{\rm acc} = C(V_{\rm GS} - V_{\rm t})$ , where C is the gate capacitance and  $V_{\rm t}$  is the threshold voltage. The source–drain current,  $I_{\rm DS}$ , can then be derived as:

$$I_{\rm DS} = \int qnv dA = \mu_{\rm FE} Q_{\rm acc} V_{\rm DS}/L_{\rm G}^2 = \mu_{\rm FE} C (V_{\rm GS} - V_{\rm t}) V_{\rm DS}/L_{\rm G}^2 \eqno(1)$$

where q is the electron charge, n is the electron concentration,  $\nu$  is the drift velocity,  $\mu_{\rm FE}$  is the field-effect mobility,  $L_{\rm G}$  is the gate length, and A is the cross-sectional area of the NW. Ballistic effects are expected to be negligible for the lengths of nanowire reported in this paper; numerical computations indicate a mean free path of  $\approx 50$  nm and scanning

# full papers

Figure 2. a) Schematic of the underlap NWFET fabricated on an oxidized Si substrate with 85/15 nm Al/Ti as the source and drain contacts, respectively, and 100/100 nm Au/SiO<sub>x</sub> as the top-gate electrode and dielectric, respectively. b) Schematic of the underlap top-gate NWFET and its equivalent capacitance circuit. c) DC circuit model of the underlap top-gate NWFETs. d) SEM image showing the "ungated" regions between the source and the drain that contribute to series resistances. Scale bar is 1  $\mu$ m.

probe microscopy (SPM) measurements on NWs grown and fabricated together with the devices we report in this paper have demonstrated ballistic or nearly ballistic transport only over distances of up to 200 nm, much shorter than the gate lengths employed here.<sup>[27,29]</sup>

The gate capacitance, *C*, is critical in obtaining the field-effect mobility. The dielectric capacitance of a top-gate NWFET is difficult to determine precisely because of the curved gate geometry and the dependence of the curvature on the oxide thickness, and the wire-to-plate capacitance model used for back-gate NWFETs is not applicable. For back-gate NWFETs and nanotube FETs, the general form of capacitance is:

$$C = 2\pi\varepsilon L_{\rm G}/\ln\left[\left(t_{\rm ox} + a + \sqrt{(t_{\rm ox} + a)^2 - a^2}\right)/a\right]$$

(2)

where  $L_{\rm G}$  is the gate length,  $\varepsilon$  is the insulator dielectric constant,  $t_{\rm ox}$  is the gate insulator thickness, and a is the nanowire radius; this can be reduced to  $C=2\pi\varepsilon L_{\rm G}/\ln\left(\frac{2t_{\rm ox}}{a}\right)$ , when  $t_{\rm ox}\!\gg\!a$ . These equations are applicable to degenerately doped NWs and have been used extensively elsewhere [3,14,16-18]. For top-gated NWFETs employed in this work, a 2D device simulator [30] was used to compute the capacitance between the metal gate and the InAs NW, and it was found that the capacitance calculated using Equation (2) is underestimated by  $\approx 10$ –14% when compared to the numerically computed capacitance; for an oxide thickness of 100 nm used in our devices, the error in using Equation (2), or its approximation, is  $\approx 13$ %. Use of the wire-to-plate capaci-

tance model would therefore lead to an overestimate of  $\approx$ 10–14% compared to the values calculated using the numerically simulated capacitance of  $\mu_{\rm FE}$ .

An additional contribution to C may arise due to the unavoidable presence of surface states in InAs. <sup>[31]</sup> To take surface and interface states into account, in analogy with a conventional metal oxide semiconductor field-effect transistor (MOSFET), <sup>[32]</sup> an interface capacitance,  $C_{\rm int}$ , is introduced in parallel with the accumulation capacitance,  $C_{\rm acc}$ , for the depletion mode InAs NWFET, as shown in Figure 2b.. The modulated electron-charge density will then be:

$$\Delta Q_{\rm acc}/A = \Delta \Psi_{\rm s} C_{\rm acc} = \Delta V_{\rm GS} C_{\rm ox}/(1+C_{\rm int}/C_{\rm acc}+C_{\rm ox}/C_{\rm acc}) \eqno(3)$$

where  $\Psi_{\rm s}$  is the surface potential at the InAs/SiO<sub>2</sub> interface, A is the area, and all capacitances are in Fcm<sup>-2</sup>.  $C_{\rm ox}/C_{\rm acc}=(\varepsilon_{\rm ox}/\varepsilon_{\rm InAs})(t_{\rm acc}/t_{\rm ox})$  is negligible in the planar approximation due to the dielectric constant difference and the large oxide thickness. A value of  $\varepsilon_{\rm ox}=3.31$  was determined experimentally for a sputtered SiO<sub>2</sub> layer from the same target;  $\varepsilon_{\rm InAs}=15.1^{[20]}$  and  $t_{\rm acc}$  and  $t_{\rm ox}=100$  nm are the accumulation layer and oxide thicknesses, respectively, with  $t_{\rm acc} \ll t_{\rm ox}$ . The accumulation capacitance can be expressed as  $C_{\rm acc}=Q_{\rm acc}/bV_{\rm t}$ , where b=2 for planar-enhancement-mode MOSFETs,  $^{[32]}$  and can be approximated as  $C_{\rm acc}=\varepsilon_{\rm InAs}/t_{\rm acc}$  where  $t_{\rm acc}$  is the separation of the accumulation charges from the surface of the nanowire due to quantum-mechanical confinement. The interface-state capacitance can be expressed as  $C_{\rm int}=qD_{\rm it}$  where  $D_{\rm it}$  is the interface-state density

in units of cm<sup>-2</sup>eV<sup>-1</sup>, distributed over an energy range within the energy bandgap of InAs. The interface-state density and its energy distribution have not yet been studied for NWs in general nor for InAs NWs in particular. If a surface-state density of  $5\times10^{12}\,\mathrm{cm^{-2}\,eV^{-1}}$  (eg.,  $10^{12}\,\mathrm{cm^{-2}}$  for an energy range of  $0.2\,\mathrm{eV}$ ) and even a very small value  $t_{\mathrm{acc}}$  of 3 nm are assumed, then  $C_{\mathrm{int}}/C_{\mathrm{acc}}=0.2$ . Thus, the term  $C_{\mathrm{int}}/C_{\mathrm{acc}}$  may not be negligible and has to be taken into account for accurate nanowire field-effect mobility calculations. However, the mobility values reported in this paper do not take into account the interface-charge-capacitance correction and are thus the lower-bound mobility values.

Straightforward circuit analysis is employed in Figure 2c to relate the quantities appearing in Equation (1) to the quantities applied at the physical electrodes of the nanowire device. Using the accumulation capacitance from Equation (3), a field-effect mobility equation can then be derived from Equation (1) as:

$$\mu_{\rm FE} = \frac{L_{\rm G}^2 V_{\rm DS}^0 (1 + C_{\rm int}/C_{\rm acc})/C}{[(V_{\rm DS}^0 - I_{\rm DS}^0 R_s)^2/g_{\rm m}^0 - (I_{\rm DS}^0)^2 R_{\rm s}^2 R_{\rm s2} - V_{\rm DS}^0 R_{\rm s2} (V_{\rm DS}^0 - 2I_{\rm DS}^0 R_{\rm s})]} \tag{4}$$

where  $g_{\rm m}^0 = \partial I_{\rm DS}^0 \partial V_{\rm GS}^0$  is the extrinsic transconductance. If the series resistances and ef-

fects of interface states are neglected, Equation (4) simplifies to:

$$\mu_{\rm FE} = g_{\rm m} L_{\rm G}^2 / CV_{\rm DS} \tag{5}$$

which is the usual expression employed to determine carrier mobility in nanowires.

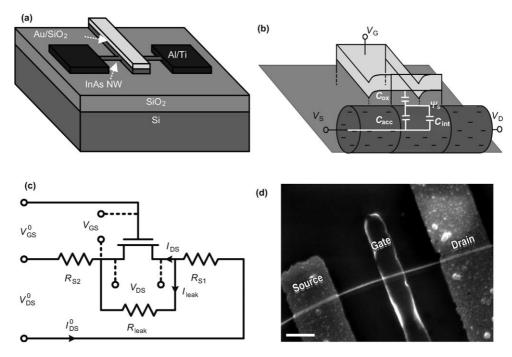

Representative  $I_{DS}^0$  versus  $V_{\rm DS}^0$  plots are shown in Figure 3 a for gate voltages  $V_{\rm DS}^0 = -2$ , 0, and +2 V, which reveals that the InAs nanowires are highly conductive with low ohmic contact resistance. The extrinsic transconductance,  $g_{\rm m}^0$ , obtained from the slope of  $I_{DS}^0$  versus  $V_{\rm GS}^0$  in the linear region (Figure 3b), is 3 μS, from which the field-effect mobility can be calculated, using Equation (4), to  $6580 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , which is the highest room-temperature field-effect mobility reported to date in any semiconductor NWFET. It should be noted that these NWFET devices exhibit hysteresis in their  $I_{DS}-V_{GS}$  characteristics (Figure 3b) that could alter the obtained extrinsic transconductance by a considerable amount (6 to 50%). We have used the lowest obtained transconductance in the mobility values reported in this paper. A detailed analysis of the hysteresis and measurement time-delay effects will be reported elsewhere.

One can also extract the current voltage characteristics,  $I_{\rm DS}$ - $V_{\rm GS}$ , intrinsic to the InAs NWFET device using circuit analysis, as shown in Figure 2c. This is shown in Figure 3c and d with the applied voltages corresponding to those in Figure 3a and b, respectively. The potential drop across the series resistances lowers  $V_{\rm DS}$  across the active portion of the NWFET device. As the source-drain current  $I_{\rm DS}$  increases with applied  $V_{GS}^0$ , the measured current  $I_{DS}^0$  increases, causing more potential drop across the series resistances. Hence,  $V_{

m DS}$  decreases with increasing  $V_{

m GS}^0$ , unlike the fixed  $V_{

m DS}^0$  applied to the physical electrodes of the device, and causes a decrease in  $I_{leak}$ . The intrinsic transconductance is calculated to be  $g_{\rm m}=\partial I_{\rm DS}/\partial V_{\rm GS}\!=\!7.7$   $\mu S$ . The differential transconductance can be incorporated along with  $V_{\mathrm{DS}}$  into  $\mu_{

m FE} = g_{

m m} L_{

m G}^2/CV_{

m DS}$  to yield mobility values (6200±1900) cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for the same device discussed above. These mobility values extracted using this conventional technique are quite consistent with those extracted using Equation (4).

Figure 3. a) Graph of  $I_{DS}^0$  versus  $V_{DS}^0$  for  $V_{DS}^0 = -2 \text{ V } (----)$ , 0 V (----), and +2 V (------) of a representative top-gate InAs NWFET. b) Graph of  $I_{DS}^0$  versus  $V_{GS}^0 = 0.5 \text{ V }$  of the same InAs NWFET. The arrows indicate the direction of the gate sweep with a sweeping rate of  $2.7 \text{ V s}^{-1}$ . c) Graph of  $I_{DS}$  versus  $V_{DS}$  for the active portion of the NWFET device, extracted from (a).  $V_{GS}^0 = -2 \text{ V } (----)$ , 0 V (----), and +2 V (----). d) Graph of  $I_{DS}$  versus  $V_{GS}$  for the top-gate NWFET, extracted at  $V_{DS}^0 = 0.5 \text{ V }$  for the same device. Device dimensions correspond to device F in Table 1.

full papers

Table 1. Summary of some representative InAs NWFET parameters and calculated field-effect mobility.

| NWFET | D<br>[nm] | L <sub>SD</sub><br>[μm] | <i>L</i> <sub>G</sub><br>[μm] | L <sub>SG</sub><br>[µm] | $R_{T}$ [k $\Omega$ ] | $R_{\rm s}$ [k $\Omega$ ] | $R_{s2}$ [k $\Omega$ ] | <i>g</i> <sub>m</sub><br>[μS] | I <sub>meas</sub><br>[μΑ] | C <sup>‡</sup><br>[fF] | <i>C</i> *<br>[fF] | $\mu^{+}$ [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | $\mu^*$ [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] |

|-------|-----------|-------------------------|-------------------------------|-------------------------|-----------------------|---------------------------|------------------------|-------------------------------|---------------------------|------------------------|--------------------|--------------------------------------------------------------|------------------------------------------------------------|

| A     | 73        | 3.87                    | 1.62                          | 1.75                    | 21.9                  | 13.14                     | 9.93                   | 1.18                          | 22.8                      | 0.419                  | 0.174              | 2630                                                         | 2260                                                       |

| В     | 49        | 3.72                    | 1.69                          | 0.986                   | 20.9                  | 11.9                      | 5.78                   | 9.06                          | 23.9                      | 0.134                  | 0.124              | 2070                                                         | 1800                                                       |

| C     | 74        | 3.72                    | 1.42                          | 1.07                    | 12.6                  | 8.15                      | 3.81                   | 1.93                          | 39.7                      | 0.132                  | 0.153              | 4800                                                         | 4160                                                       |

| D     | 63        | 3.66                    | 1.52                          | 1.15                    | 11.9                  | 7.36                      | 3.9                    | 1.67                          | 42.4                      | 0.132                  | 0.154              | 4070                                                         | 3500                                                       |

| E     | 65        | 3.41                    | 1.45                          | 1.21                    | 16                    | 9.64                      | 5.85                   | 0.88                          | 31.2                      | 0.128                  | 0.147              | 1830                                                         | 1590                                                       |

| F     | 68        | 3.48                    | 1.30                          | 1.04                    | 13.2                  | 8.63                      | 4.31                   | 3.04                          | 38                        | 0.116                  | 0.133              | 7500                                                         | 6580                                                       |

| G     | 47        | 3.64                    | 1.61                          | 1.25                    | 25.5                  | 14.6                      | 8.87                   | 1.88                          | 19.6                      | 0.127                  | 0.145              | 4320                                                         | 3770                                                       |

Table 1 summarizes the extracted field-effect mobilities of seven representative devices; the NW diameters (D), source-drain lengths  $(L_{\rm SD})$ , gate lengths  $(L_{\rm G})$ , and gatesource lengths  $(L_{SG})$  were measured using SEM.  $R_{T}$  is the total device resistance and is equal to the sum of the NW resistance  $(R_{NW})$  and the contact resistance  $(R_c)$ . The total series resistance  $R_s$  can be calculated using  $R_s = (R_T - R_c)$ - $(L_{SD}-L_G)/L_{SD}+R_c$ . The source series resistance  $R_{s2}$  can be calculated using  $R_{s2} \! = \! (R_s \! - \! R_c) L_{SG} \! / (L_{SD} \! - \! L_G) + R_c \! / 2$ . The measured current  $I_{\text{meas}}$  is that measured at  $V_{\text{DS}}^0 = 0.5 \text{ V}$ ;  $C^{\dagger}$  is the capacitance calculated using Equation (2),  $\mu^{\dagger}$  is the mobility calculated using  $C^{\dagger}$  and Equation (4);  $C^{*}$  is the numerically computed capacitance using Silvaco software, and  $\mu^*$  is the mobility calculated using  $C^*$  and Equation (4). The field-effect mobility in these InAs nanowires is much lower than the bulk InAs mobility (33 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) due to surface scattering but higher than that typically measured for the accumulated free-electron gas on the InAs surface  $(2000-3000 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1})$ . [33,34] Such an intermediate value is expected, given the combination of surface and bulk electron transport likely to be present in these NWs. We anticipate that carrier mobility can be increased by surface passivation<sup>[13,35]</sup> or in heterostructure core/shell NWs.<sup>[15]</sup> Table 1 also lists the mobilities calculated using the capacitance given by the wire-to-plate model, which quantifies the discrepancy compared to those obtained using the numerical simulated capacitance.

The modulated carrier concentration in the NWFET channel underneath the gate can be calculated from Equation (1) and is given by:

$$\Delta n_{\rm channel} = \frac{I_{\rm DS} L_{\rm G}}{q \mu_{\rm FE} V_{\rm DS} A} \tag{6}$$

The typical calculated  $\Delta n_{\rm channel}$  values are  $\approx 10^{17}$ – $10^{18}$  cm<sup>-3</sup> with a leakage carrier concentration  $n_{\rm leak} \approx 10^{16}$ – $10^{17}$  cm<sup>-3</sup>. The entire carrier concentration n is expected to be the sum of these two quantities.

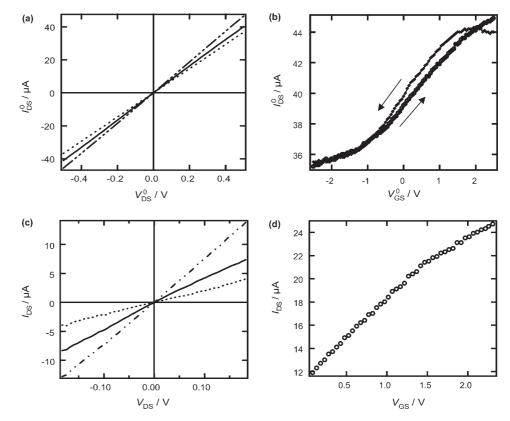

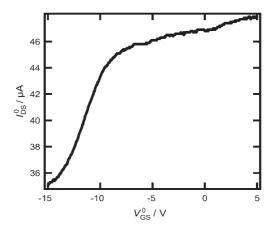

Finally, back-gate InAs NWFETs were also fabricated and back-gate measurements performed (Figure 4) to compare our top-gate model with the back-gate model and to enable a fair comparison of our results with carrier mobilities reported in other NW studies. A field-effect mobility of  $\mu_{\rm FE} = 2740~{\rm cm^2\,V^{-1}\,s^{-1}}$  was obtained using Equation (5) and the wire-to-plate capacitance model, and corresponds to a transconductance of 2  $\mu$ S. This value is significantly higher than the mobility values reported for other NWs listed in

Table 2 and is comparable to that of the free-electron gas on the InAs surface, which suggests an increased influence of surface states due to poor physical contact between the nanowire and the SiO<sub>2</sub> substrate compared to the top-gate NWFETs, and substantial gate coupling to the source and drain electrodes

Figure 4. Graph of back-gate  $I_{\rm DS}-V_{\rm GS}$  at  $V_{\rm DS}=0.5$  V for the same device shown in Figure 3.

**Table 2.** Comparison of different semiconductor NWFETs (nonpassivated nanowires).

| NW   | Carrier | $\mu$ [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] |                     | J <sub>DS</sub> <sup>[a]</sup> [A cm <sup>-2</sup> ] | $I_{\rm on}/I_{\rm off}$ | Reference |

|------|---------|----------------------------------------------------------|---------------------|------------------------------------------------------|--------------------------|-----------|

| Ge   | h       | 600                                                      | 3×10 <sup>18</sup>  | ≈ 10 <sup>4</sup>                                    | 10 <sup>3</sup>          | 11        |

| Si   | h       | 560                                                      |                     | $1.41 \times 10^{5}$                                 | $10^{4}$                 | 13        |

| GaN  | e       | 650                                                      | $10^{18} - 10^{19}$ | $2.88 \times 10^{5}$                                 |                          | 14        |

| ZnO  | e       | $13\pm5$                                                 | $5 \times 10^{17}$  | $3.74 \times 10^{3}$                                 | $10^5 - 10^7$            | 16        |

| InAs | e       | $6200 \pm 1900$                                          | $10^{17} - 10^{18}$ | $10^6 - 10^7$                                        | 2-100                    | This work |

[a] At  $V_{DS} = 0.5$  V and  $V_{GS} = 0$  V, or the maximum available values.

### 3. Conclusions

In summary, we have fabricated and characterized underlap top-gate and global back-gate InAs NWFETs, and demonstrated the highest semiconductor nanowire electron mobility reported to date. For top-gate NWFETs, we have developed a model that allows a more accurate estimation of field-effect mobility and carrier concentration in semiconductor nanowires by taking into account series and leakage resistances, interface-state capacitance, and top-gate geometry for oxide-capacitance calculation. In particular, we have

derived a new mobility equation for the analysis of the underlap gate NWFET device. A peak mobility value of  $6580~\text{cm}^2\text{V}^{-1}\text{s}^{-1}$  at low drift fields of  $\approx 1.5~\text{kV}\,\text{cm}^{-1}$  was measured in a top-gate InAs NWFET, and measurements on several devices yielded a representative average mobility value of  $\approx 3400~\text{cm}^2\text{V}^{-1}\text{s}^{-1}$ . Both values represent lower bounds on the calculated mobility, which are conservative estimates because 1) the lowest possible ohmic contact resistance was used; 2) the lower extracted transconductance from the hysteretic NWFET measurements was employed for mobility calculation, and 3) the effect of surface states has not been taken into account. These results demonstrate the promising potential of using InAs nanowires for high-speed nanoelectronics.

### 4. Experimental Section

The InAs NWs were grown in a horizontal growth tube on  $600\text{-nm SiO}_2\text{-}n^+\text{-Si}$  substrates by metal—organic chemical vapor deposition. Au colloids (40-nm diameter, Ted Pella) were dispersed from solution on cleaned substrates pretreated with Polyt-Lysine. The substrates were then loaded into the growth chamber and the temperature was ramped to the final growth temperature (350 °C) in a  $H_2$  atmosphere. Arsine (148  $\mu$ mol min $^{-1}$ , 10% As $H_3$  in  $H_2$ ) and Trimethylindium (TMIn, 6  $\mu$ mol min $^{-1}$ ) precursors were then introduced into 1.2 Lmin $^{-1}$   $H_2$  carrier gas with an input V:III ratio of 25 and a chamber pressure maintained at 100 Torr. The samples were then cooled to room temperature in an As $H_3$  atmosphere. The single-crystal InAs NWs were 30–75 nm in diameter and 20–30  $\mu$ m long after a 15-min growth time.

A sonication of 7 s in ethanol solution was used to suspend the nanowires in the solution; they were then transferred to a 600-nm SiO<sub>2</sub>-n+Si substrate with a prepatterned indexed grid with alignment marks. Optical microscopy was used to determine the locations of the randomly dispersed nanowires on this grid structure. Patterning of contacts by EBL followed by 15-nm Ti/85-nm Al metallization and a standard liftoff process were used to create ohmic contacts to the nanowires. Gate-pattern definition by EBL, sputtering of 100 nm SiO<sub>2</sub>/100 nm Au, and subsequent lift-off were used to form top-gate structures. Current-voltage characteristics were then obtained with an HP4155 semiconductor parameter analyzer in air at room temperature. The device dimensions were measured after electrical measurements under the highest magnification (x 300 000) using a FEI XL 30 Environmental SEM operating at an acceleration voltage of 10 kV.

## **Acknowledgements**

This work was supported in part by the Office of Naval Research (ONR Nanoelectronics), the National Science Foundation (ECS-0506902), and Sharp Labs of America. We thank

Dr. Yat Li at Harvard for help with TEM studies, Prof. Peter M. Asbeck for thorough manuscript reading, and Lingquan Wang and Adam Conway for helpful discussions.

- [1] C. M. Lieber, MRS Bull. 2003, 28, 486.

- [2] Y. Xia, P. Yang, Y. Sun, Y. Wu, B. Mayers, B. Gates, Y. Yin, F. Kim, H. Yan, Adv. Mater. 2003, 15, 353.

- [3] X. Duan, Y. Huang, Y. Cui, J. Wang, C. M. Lieber, *Nature* 2001, 409, 66.

- [4] Y. Huang, X. Duan, Y. Cui, L. J. Lauhon, K.-H. Kim, C. M. Lieber, Science 2001, 294, 1313.

- [5] Z. Zhong, D. Wang, Y. Cui, M. W. Bockrath, C. M. Lieber, *Science* 2003, 302, 1377.

- [6] M. Gudiksen, L. J. Lauhon, J. Wang, D. Smith, C. M. Lieber, Nature 2002, 415, 617.

- [7] J. Wang, M. S. Gudiksen, X. Duan, Y. Cui, C. M. Lieber, *Science* 2001, 293, 1455.

- [8] M. H. Huang, S. Mao, H. Feick, H. Yan, Y. Wu, H. Kind, E. Weber, R. Russo, P. Yang, *Science* 2001, 292, 1897.

- [9] X. Duan, Y. Huang, R. Agarwal, C. M. Lieber, *Nature* 2003, 421, 241.

- [10] Y. Cui, Q. Wei, H. Park, C. M. Lieber, Science 2001, 293, 1289.

- [11] Q. Wang, A. Javey, R. Tu, H. Dai, H. H. Kim, P. McIntyre, T. Krishnamohan, K. Saraswat, Appl. Phys. Lett. 2003, 83, 2432.

- [12] D. Wang, Y. Chang, Q. Wang, J. Cao, D. Farmer, R. Gordon, H. Dai, J. Am. Chem. Soc. 2005, 126, 11602.

- [13] Y. Cui, Z. Zhong, D. Wang, W. Wang, C. M. Lieber, *Nano Lett.* **2003**, *3*, 149.

- [14] Y. Huang, X. F. Duan, Y. Cui, C. M. Lieber, Nano Lett. 2005, 2, 101.

- [15] S. A. Dayeh, D. Aplin, X. Zhou, P. K. L. Yu, E. T. Yu, D. Wang, 47<sup>th</sup> TMS Annual Electronic Materials Conference, Santa Barbara, 2005.

- [16] T. Bryllert, L. Samuelson, L. Jensen, L. Wernersson, DRC Proc. 2005, 1, 157.

- [17] J. Goldberger, D. Sirbuly, M. Law, P. Yang, J. Phys. Chem. B 2005, 109. 9.

- [18] H. T. Ng, J. Han, T. Yamada, P. Nguyen, Y. P. Chen, M. Meyyappan, Nano Lett. 2004, 4, 1247.

- [19] D. Zhang, C. Li, S. Han, X. Liu, T. Tang, W. Jin, C. Zhou, Appl. Phys. Lett. 2003, 82, 112.

- [20] S. M. Sze, Physics of Semiconductor Devices (2nd ed.) Wiley Interscience, 1981.

- [21] C. A. Mead, W. G. Spitzer, Phys. Rev. Lett. 1963, 10, 471.

- [22] M. Noguchi, K. Hirakawa, T. Ikoma, Phys. Rev. Lett. 1991, 66, 2243.

- [23] J. M. Woodall, J. L. Freeouf, G. D. Pettit, T. Jackson, P. Kircher, J. Vac. Sci. Technol. 1981, 19, 626.

- [24] M. T. Björk, B. J. Ohlsson, C. Thelander, A. I. Persson, K. Deppert, L. R. Wallenberg, L. Samuelson, Appl. Phys. Lett. 2002, 81, 4458

- [25] C. Thelander, T. Martensson, M. T. Bjork, B. J. Ohlsson, M. W. Larsson, L. R. Wallenberg, L. Samuelson, Appl. Phys. Lett. 2003, 83, 2052.

- [26] Y. J. Doh, J. A. van Dam, A. L. Roest, E. P. A. M. Bakkers, L. P. Kouwenhoven, S. De Franceschi, *Science* 2005, 309, 272.

- [27] X. Zhou, S. A. Dayeh, D. Aplin, D. Wang, and E. T. Yu, J. Vac. Sci. Technol. A 2006, 24, 2036.

- [28] S. Datta, Electronic Transport in Mesoscopic Systems, Cambridge University Press, Cambridge, UK, 1995.

- [29] X. Zhou, S. A. Dayeh, D. Aplin, D. Wang, E. T. Yu, Appl. Phys. Lett. 2006, 89, 053113.

- [30] http://www.silvaco.com/products/device simulation/at-las.html. The  ${\rm SiO_2}$  layer was sputtered on a rotating stage at

- 60 rpm and uniform coverage along the circumference of the nanowire was used in the simulation.

- [31] J. M. Ziman, *Principles of the Theory of Solids* (2nd ed.), Cambridge University Press, Cambridge, UK, **1972**.

- [32] Y. Taur, T. H. Ning, *Fundamentals of Modern VLSI Devices* (1st ed.) Cambridge University Press, Cambridge, UK, **1998**.

- [33] E. Yamaguchi, M. Minakata, Appl. Phys. Lett. 1983, 43, 965.

- [34] Y. Tsuji, T. Mochizuki, T. Okamoto, Appl. Phys. Lett. 2005, 87, 62103.

- [35] W. Park, J. S. Kim, G. Yia, M. H. Bae, H. J. Lee, Appl. Phys. Lett. 2004, 85, 5052.

Received: July 26, 2006 Published online on December 5, 2006