# A Near-Zero-Power Wake-Up Receiver Achieving —69-dBm Sensitivity

Po-Han Peter Wang<sup>®</sup>, Student Member, IEEE, Haowei Jiang, Student Member, IEEE,

Li Gao, Student Member, IEEE, Pinar Sen, Student Member, IEEE, Young-Han Kim, Fellow, IEEE,

Gabriel M. Rebeiz, Fellow, IEEE, Patrick P. Mercier, Senior Member, IEEE, and Drew A. Hall, Member, IEEE

Abstract—This paper presents the design of a wake-up receiver (WuRX) that both improves sensitivity and reduces power over prior art through a multi-faceted design featuring an off-chip impedance transformation network with large passive voltage gain, an active envelope detector with high input impedance to facilitate large passive voltage gain, a low-power precision comparator, and a low-leakage digital baseband correlator. Implemented in a 180-nm silicon on insulator CMOS process using dynamic threshold-voltage MOSFET (DTMOS) devices, the OOK-modulated WuRX operates at 113.5 MHz and achieves a sensitivity of -69 dBm, while consuming just 4.5 nW from a 0.4-V supply.

Index Terms—Low-power wide area network (LPWAN), low-power wireless, near-zero-power, wake-up radios, wake-up receivers (WuRXs).

## I. Introduction

THE high-power consumption of conventional low-power wide area network (LPWAN) receivers employed in applications such as smart meters, environmental sensors, threat monitors, and other Internet of Things (IoT) like applications often dictates overall device battery life. Even though many such applications communicate at low-average throughputs, the power of the radio can be high due to the need for frequent network synchronization [1]. To reduce the power consumption, wake-up receivers (WuRXs), which tradeoff sensitivity and/or data rate for low-power operation, ideally without seriously compromising interference resilience, have been proposed to monitor the RF environment and wake up a high-performance (and higher power) conventional radio upon the reception of a predetermined wake-up packet.

The two most important metrics for WuRXs used in low-average throughput applications are the power consumption and sensitivity, as the power of always-on WuRXs ultimately determines the battery life of low-activity devices, while sensitivity determines the communication distance and, therefore, the deployment cost via the total number of nodes required to achieve a given network coverage. Typically, sensitivity

Manuscript received June 30, 2017; revised January 29, 2018 and February 21, 2018; accepted February 22, 2018. Date of publication April 19, 2018; date of current version May 24, 2018. This paper was approved by Associate Editor Kenichi Okada. This work was supported by DARPA under Contract HR0011-15-C-0134. (Corresponding author: Drew A. Hall.)

The authors are with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA (e-mail: pmercier@ucsd.edu; drewhall@ucsd.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2018.2815658

and power consumption tradeoff with one another, making the design of WuRXs that simultaneously achieve both challenging. Interference resilience is also an important metric for WuRXs, since false alarms cause unwanted power dissipation in sensor nodes, while missed detections result in sensor network malfunctions. Unlike conventional mobile receiver design, metrics such as physical size and data rate can often be exploited to improve sensitivity or reduce power, as will be shown shortly.

WuRXs can be loosely classified into two categories based on whether or not a mixer is present. Mixer-based WuRXs tend to utilize a local oscillator (LO), generated via a phase-locked loop (PLL) [2], injection locking from a crystal or high-Q resonator [3], or an uncertain freerunning ring oscillator [4], [5] or LC oscillator [6], to mix down incoming RF energy to a known [2], [3] or uncertain [4]-[6] intermediate frequency (IF). Mixing down to an IF allows more efficient amplification than at RF, and thus, such approaches often forgo inclusion of any RF low noise amplifiers (LNAs), at the expense of an increased system noise figure. This approach is advantageous in terms of sensitivity and interference resilience, as it is generally possible to design sharp, yet low power, IF filters to knock out RF and circuit noise, along with interfering blockers. However, LO generation requires significant power, and thus, mixer-based architectures are generally used in applications where  $\mu W$  power levels are acceptable.

On the other hand, direct envelope detection architectures, which forgo LO generation/mixing and instead demodulate directly to baseband, can achieve much lower power than mixer-based designs [7]–[9]. However, since envelope detectors (EDs) demodulate all energy present at their inputs to baseband, such architectures tend to accumulate significant noise and interference, making their sensitivity generally inferior to mixer-based architectures.

This paper presents the design of a WuRX that targets LPWAN applications and, therefore, attempts to achieve both low power and high sensitivity with reasonable interference resilience through a combination of techniques including careful selection of the carrier frequency and data rate, inclusion of a high-Q RF impedance transformer/filter that delivers passive voltage gain as well as interference filtering, a high input impedance and high conversion gain ED, a precise, yet low-power, regenerative comparator, and an optimized digital correlator that provides coding gain while combating false

alarms caused by interferers. This architecture was originally presented in [10]; this paper provides significant additional circuit design details and measurement results. The overall WuRX architecture is presented in Section II, while Section III describes the implemented off-chip transformer and circuits. Section IV presents measurement results, followed by a figure-of-merit (FoM) landscape of state-of-the-art WuRXs in Section V. Finally, Section VI concludes this paper.

## II. WAKE-UP RECEIVER ARCHITECTURE

### A. Overview

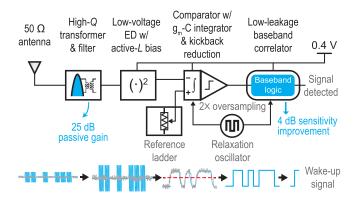

The architecture of the proposed WuRX is shown in Fig. 1. The primary optimization objective of this design was to minimize power. This motivated the use of a direct ED WuRX architecture operating at a low supply voltage (0.4 V in this work). However, the secondary objective was to achieve sensitivity that approaches that of a mixer-based WuRX architecture, while not significantly compromising tolerance to interferers. This was accomplished through a number of architectural and circuit design techniques described as follows.

## B. Direct Envelope Detection RF Front-End Optimizations

Direct ED architectures demodulate all input RF energy to baseband, and thus, any interferers within the input RF bandwidth can inhibit proper reception. In addition, the lack of an LNA together with very low-power demodulating circuits means that the baseband circuit noise often dominates, thereby ultimately limiting the WuRX sensitivity. Fortunately, these two problems, i.e., interference and baseband circuit noise, can be overcome via the following techniques:

- 1) Minimizing Interference via High-Q Filtering: To reduce the impact of in-band blockers in direct-ED or uncertain-IF mixer-based architectures, a high-Q narrowband filter is needed to minimize RF bandwidth and block interferers. Most prior-art low-power radios accomplish narrowband filtering by utilizing high-Q mechanical resonators, which offer attractive narrow filtering capability at 1–3 GHz [4], [11]. In this design, however, to attain the highest possible Q for sharp filtering, and, as will be seen shortly, to achieve a large impedance transformation ratio from a 50- $\Omega$  source as well as wide communication range, a carrier frequency in the 100-MHz range was selected for use near the FM radio band. Therefore, a high-Q filter (and, as will be described shortly, transformer) was designed out of lumped components directly.

- 2) Minimizing Baseband Circuit Noise via Passive RF Voltage Amplification: EDs are inherently non-linear elements. Unlike linear mixers used for down-conversion, the squaring operation of an ED converts pre-ED noise down to baseband via two mechanisms: self-mixing of noise and noise convolved with the input signal [12]. Since most ultralow-power WuRXs forgo active gain before the ED, sensitivity is typically limited by baseband noise. Therefore, to improve sensitivity without a power penalty, most direct ED WuRX designs strive to achieve as much passive voltage gain in the matching network as possible. This is typically achieved by designing the ED to have a large input impedance, and matching this large impedance to 50  $\Omega$  via an impedance transformation network.

Fig. 1. Overview of the proposed WuRX.

Prior work has shown 5 and 12 dB of passive voltage gain which, when coupled to either a rectifier or an active ED, achieved sensitivities of -45.5 and -41 dBm at 12.5 and 100 kbps at powers of 116 and 98 nW, respectively [7], [8]. Thus, direct ED systems can achieve ultralow-power operation, yet without large RF voltage gain and low-noise baseband circuits, do so at limited sensitivities.

To address the aforementioned issues, the proposed WuRX incorporates an ED with a high input impedance that, combined with a high-Q impedance transformer, facilitates up to 25 dB of passive voltage gain at RF before being demodulated by the ED, thus directly resulting in a 25-dB improvement in sensitivity compared to the exclusion of this transformer. Furthermore, the ED is designed to support high conversion gain to further reduce the impact of baseband circuit noise (i.e., to increase the SNR).

# C. Baseband Bandwidth Considerations

There are two primary classes of applications where WuRXs can be useful: 1) high-average throughput applications with asynchronous communication needs where WuRXs are primarily used to eliminate the need for precision watchdog timers that perform network synchronization and 2) low-average throughput applications where the network is largely idle, waiting for an event to occur such as in infrastructure, perimeter, and health alarm monitoring. In high throughput applications, it is important to minimize wake-up detection latency, set in part by the WuRX data rate, so as to not adversely affect the average network throughput. In low throughput applications, wake-up latency (and thus the data rate of the WuRX), is less important, as long latency does not adversely affect the overall throughput needed. Most conventional WuRX designs target the first class of applications; this paper instead focuses on the design of WuRXs used in low-average throughput LPWAN applications. One of the key ideas of a LPWAN is to leverage the reduced data rate (and thus integrated baseband noise) to improve sensitivity and enable wide communication range. For example, LoRaWAN utilizes a 300 bps to 50 kbps data rate, whereas Sigfox is only 100 to 600 bps. Therefore, a 300 bps data rate was selected for this design.

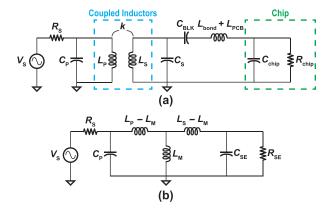

Fig. 2. Schematics of (a) transformer/filter and (b) equivalent circuit model.

# D. Digital Baseband Processing

The received RF signal employed in this design is modulated with a custom designed 16-bit sequence. After rectification the demodulated signal is  $2\times$  oversampled and digitized by a 1-bit regenerative comparator. The output of the comparator feeds a digital correlator that computes the Hamming distance between the received and stored sequences. When the Hamming distance is below a programmable threshold ( $H_{th}$ ), a wake-up signal is generated. It will be shown in Section IV that the use of this wake-up sequence provides additional coding gain that improves the sensitivity of the proposed WuRX. Moreover, the correlator prevents false alarms caused by unwanted jammers. An on-chip relaxation oscillator provides the required 600-Hz clock.

## III. CIRCUIT IMPLEMENTATION

# A. Transformer/Filter

The purposes of the transformer/filter is to impedance transform a  $50-\Omega$  source impedance to a much larger value to facilitate passive voltage gain, while also performing high-Q RF filtering. The schematic of the implemented transformer/filter is shown in Fig. 2(a) where  $R_S$  is the 50- $\Omega$ source impedance. The primary stage resonator is formed by  $L_P$  and  $C_P$ , while the secondary stage is formed by  $L_S$  and  $C_S$ , with k denoting the coupling coefficient between  $L_P$  and  $L_S$ .  $C_{\rm chip}$  and  $R_{\rm chip}$  are the equivalent input impedance of the chip at the carrier frequency, which connects to the transformer/filter via a large ac-coupling capacitor, C<sub>BLK</sub>, and a small parasitic inductor from the printed circuit board (PCB) trace and bondwire. Both the primary and secondary stage tanks resonate at the same frequency,  $f_{RF} = 113.5$  MHz. Departing from a traditional two-port RF filter, which has 50  $\Omega$ matching at both ports, the proposed transformer/filter not only provides a second-order filter response for interference rejection but also realizes impedance transformation between the two ports to achieve passive voltage gain. To analyze the circuit, an equivalent circuit model is derived as shown in Fig. 2(b).  $L_{\rm M}$  is determined by k and can be written as [13]

$$L_{\rm M} = k \cdot \sqrt{L_{\rm P} L_{\rm S}} = k \cdot L_{\rm S} \cdot \sqrt{\frac{1}{N}} \tag{1}$$

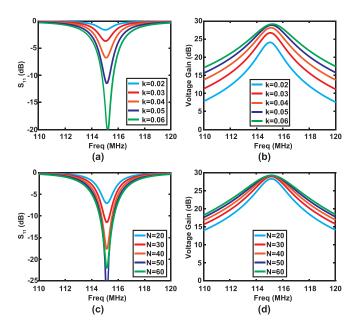

Fig. 3. (a)  $S_{11}$  versus k. (b) Voltage gain versus k. (c)  $S_{11}$  versus N. (d) Voltage gain versus N.

where N is the turn ratio between  $L_{\rm P}$  and  $L_{\rm S}$ .  $C_{\rm SE}$  and  $R_{\rm SE}$  are the equivalent capacitor and resistor of the secondary stage, with  $C_{\rm SE} = C_{\rm S} + C_{\rm chip}$  and  $R_{\rm SE} = R_{\rm EQ,P}||R_{\rm chip}||R_{\rm chip}||R$

$$Gain_{max} = \sqrt{\frac{R_{SE}}{R_{S}}} = \sqrt{\frac{R_{EQ,P}||R_{chip}}{R_{S}}}.$$

(2)

To get large passive voltage gain, a large  $R_{\rm EQ,P}$  must be achieved by either increasing Q or  $L_{\rm S}$  for a given  $C_{\rm SE}$ . Since Q can only be pushed so high using practical inductors,  $L_{\rm S}$  is the only practical tunable parameter. There are two things that limit the achievable value of  $L_{\rm S}$ : 1) the chip input capacitance,  $C_{\rm chip}$  and 2) the self-resonant frequency of the inductor. With  $C_{\rm S}=0$  pF and  $C_{\rm chip}=1.8$  pF, the maximum  $L_{\rm S}$  is 1.06  $\mu$ H. Due to the size of the required inductor, it must be off-chip. For commercial inductors with high Q, self-resonance typically occurs when  $\omega L\approx 1,400~\Omega$ . To account for variation in  $C_{\rm chip}$  and on-board parasitics,  $\omega L=520~\Omega$  was chosen. From the datasheet of the selected inductor [14], a Q of 150 can be obtained at 115 MHz, and thus  $R_{\rm EO,P}<78~{\rm k}\Omega$ .

After determining the value of  $L_{\rm S}$  and  $C_{\rm S}$ , we considered the coupling coefficient k and the turn ratio N, both of which affect the input matching and passive voltage gain. To have a sharp filter response for out-of-band interference rejection, k should be small and Q should be large [15]. Fig. 3(a) and (b) shows calculated  $S_{11}$  and voltage gain of the transformer/filter varying k with N fixed to be 30. When k is increased from 0.02 to 0.06, the input matching gets better and the voltage gain increases. However, the filter bandwidth also increases. Fig. 3(c) and (d) shows calculated  $S_{11}$  and voltage gain varying N with k=0.05. When N is increased from 20 to 60, the voltage gain does not increase much, but with considerably

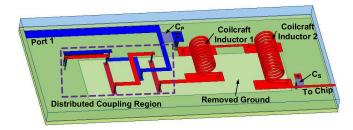

Fig. 4. 3-D model of the transformer/filter.

larger filter bandwidth. Therefore, k = 0.05 and N = 30 were chosen as a compromise between input matching, voltage gain, and filter bandwidth. Calculations show that  $S_{11}$  is better than -10 dB with a passive voltage gain of 28.9 dB and a 3-dB bandwidth of 2.4 MHz.

The key challenge in implementing the proposed transformer/filter is to control the coupling despite the large difference in inductance (24 and 720 nH). Implementing the inductors using only lumped elements would make it very hard to control the coupling through positioning, whereas only distributed inductors would take too much area. As such, we used a combination of lumped inductors (160 and 220 nH from Coilcraft) and a distributed inductor to realize  $L_S$  and a distributed inductor to realize  $L_P$ , which has three advantages. First,  $L_{\rm S}$  is realized by both distributed and lumped inductors, thus the value can be large. Second, the coupling is realized by the distributed parts of  $L_P$  and  $L_S$ , and thus, k is determined by the length and gap of the coupling PCB traces. With modern PCB fabrication techniques, this coupling can be controlled precisely, which is crucial since k affects both passive gain and filter bandwidth. Third, the use of both lumped and distributed inductors provides more freedom to design the transformer. For example, the center frequency can be easily tuned by replacing lumped components, which is an advantage compared to mechanical resonators [4], [11].

Fig. 4 shows the 3-D model of the transformer/filter. To reduce the dielectric loss, a Rogers RO4003C substrate was used ( $\epsilon_{\rm r}=3.55$ , thickness of 20 mil, and a loss tangent of 0.0027). From HFSS simulations, we found that at 115 MHz,  $L_{\rm P}$  and  $L_{\rm S}$  are 28 and 756 nH, respectively, and k=0.05. All of the component values are close to the desired values from calculation. The simulated voltage gain was 26.6 dB with a bandwidth of 2.2 MHz.

# B. Envelope Detector

To take full advantage of the gain provided by the transformer/filter, the ED must provide a large enough input resistance  $R_{\rm chip}$  so as to not to degrade the corresponding  $R_{\rm EQ,P}$ . Although a passive N-stage RF rectifier [7], [9] is a tempting choice (due to the zero power consumption), it is difficult to achieve high enough  $R_{\rm chip}$ . Thus, in this work, an active ED was selected. A transistor biased in the sub- $V_{\rm t}$  region can not only operate with a low supply voltage and low-power consumption but also provides an exponential voltage–current relationship. Assuming that the transistor is operating in the sub- $V_{\rm t}$  saturation region (i.e.,  $V_{\rm DS} > 100$  mV) with

Fig. 5. (a) Schematic of proposed active-*L*-biased ED. (b) Active-*L* biasing circuit model and Bode plot of ED output impedance.

negligible drain-induced barrier lowering (DIBL), the current can be written as [16]

$$i_{\rm DS} = \mu C_{\rm ox} \frac{W}{L} (n-1) V_{\rm T}^2 e^{\frac{v_{\rm GS} - V_{\rm t}}{nV_{\rm T}}}$$

(3)

where  $\mu$  is the mobility,  $C_{\rm ox}$  is the oxide capacitance, W is the transistor width, L is the transistor length, n is the sub- $V_{\rm t}$  slope factor,  $V_{\rm T}$  is the thermal voltage  $(k_{\rm B}T/q)$ , and  $v_{\rm GS}$  is the gate-to-source voltage. This exponential relationship results in a second-order non-linearity used for the desired ED functionality. The second order transconductance is given as

$$g_{\rm m2} = \frac{1}{2} \cdot \frac{\partial^2 i_{\rm DS}}{\partial v_{\rm GS}^2} = \frac{I_{\rm DS}}{2(nV_{\rm T})^2}.$$

(4)

In an silicon on insulator (SOI) process, the floating body can be connected to the gate directly without using deep n-well devices, commonly referred to as the dynamic threshold-voltage MOSFET (DTMOS) configuration [17], to achieve additional second order non-linearity via threshold voltage modulation. The additional transconductance can be derived as

$$g_{\text{mb2}} = \frac{1}{2} \frac{\partial^2 i_{\text{DS}}}{\partial v_{\text{BS}}^2} = (n-1)^2 \cdot g_{\text{m2}}.$$

(5)

For the process used in sub- $V_t$ ,  $n \approx 1.4$ , meaning that the DTMOS configuration provides an additional 16% transconductance compared to gate input only.

Conventional common source ED biasing schemes use either a diode-connected load or a resistive load. Unfortunately, the diode connected load results in a low output resistance (similar to a source follower ED) and only achieves high conversion gain with large input signals, while a resistive load has limited conversion gain with a 0.4-V supply voltage. Other techniques such as a cascode level shifter provide high output resistance, but require extra voltage headroom [8] not compatible with the employed 0.4-V supply.

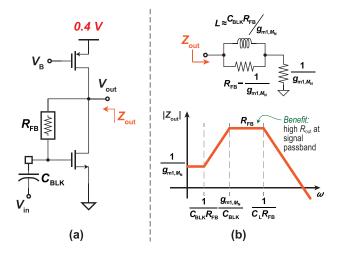

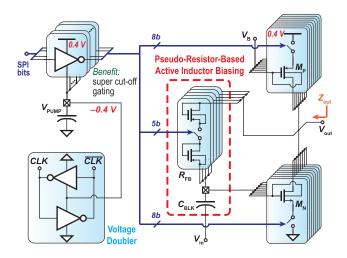

To address the aforementioned issues, an active-L self-biased ED was designed [Fig. 5(a)]. The feedback resistor sets the dc voltage for both the gate and drain nodes of the

Fig. 6. Full schematic of the proposed low-voltage active-*L*-biased DTMOS ED with boosted binary-weighted SPI control.

input transistor and serves as the output impedance. The output impedance can be written as

$$Z_{\text{out}} = \left(\frac{g_{\text{m1}} + sC_{\text{BLK}}}{1 + sC_{\text{BLK}}R_{\text{FB}}} + \frac{1}{r_{\text{o}}} + sC_{\text{L}}\right)^{-1} \tag{6}$$

where  $g_{\rm m1}$  is the transconductance of the NMOS,  $C_{\rm BLK}$  is the ac-coupling capacitor,  $R_{\rm FB}$  is the feedback resistor,  $r_{\rm o}$  is the small-signal intrinsic output resistance of the transistor, and  $C_{\rm L}$  is the capacitance at the output node. Assuming  $r_{\rm o}\gg 1/g_{\rm m1}$  and  $r_{\rm o}\gg R_{\rm FB}$  because of the low current (5 nA in this design, which results in  $r_{\rm o}\approx 1~{\rm G}\Omega$  and  $1/g_{\rm m1}\approx 7~{\rm M}\Omega$ ),  $C_{\rm BLK}\gg C_{\rm L}$ , and  $C_{\rm BLK}/g_{\rm m1}\gg C_{\rm L}R_{\rm FB}$ , (6) can be simplified to

$$Z_{\text{out}} \simeq \frac{1}{g_{\text{m1}}} \cdot \frac{1 + sC_{\text{BLK}}R_{\text{FB}}}{\left(1 + s\frac{C_{\text{BLK}}}{g_{\text{m1}}}\right)(1 + sC_{\text{L}}R_{\text{FB}})}$$

(7)

which contains two poles and one zero. The equivalent circuit model and Bode plot of  $Z_{\rm out}$  are shown in Fig. 5(b). It can be seen that the output impedance is boosted to  $R_{\rm FB}$  within the signal passband due to the active-L biasing, which leads to higher conversion gain. Since non-return-to-zero (NRZ) signaling is used, the high pass corner must be low enough to not attenuate the signal power and was set to 20 mHz in this design for <0.01 dB SNR degradation from baseline wander. Therefore, an off-chip  $C_{\rm BLK}$  was used as a dc block and incorporated into the bias network.

The full ED schematic is shown in Fig. 6. Due to significant process variation in sub- $V_t$  circuits, both  $M_N$  and  $M_P$  were designed to have 8-bit binary-weighted tuning capability. To reduce the leakage of unused  $M_N$  via super-cutoff biasing, and to turn on  $M_P$  strongly, a voltage doubler [18] was designed to provide -0.4 V, saving up to 3 nA in simulation (in the TT corner). Because of the high required value of the feedback resistor, a MOS-bipolar-pseudoresistor was used instead of a poly resistor to prevent high capacitive loading of the input node at RF, which ultimately limits the achievable inductor value of the second stage of the transformer/filter, and therefore passive voltage gain. For the same reasons as above,

Fig. 7. Simulated ED output SNR versus integrated comparator noise voltage for different biasing schemes.

and to make the baseband bandwidth tunable, the pseudoresistor was implemented with 5 binary-weighted bits. Since the baseband bandwidth is 300 Hz, all critical transistors were sized to trade-off the contributions of 1/f noise while minimizing parasitic capacitance at the output node, the latter of which ultimately limits the achievable  $R_{\rm FB}$  to  $\sim 100~{\rm M}\Omega$ .

The demodulated output signal of the ED is

$$v_{\text{out}} = \text{Conv}_{\text{Gain}} \cdot v_{\text{in}} = \frac{k_{\text{ED}}}{2} \cdot v_{\text{in}}^2$$

(8)

where  $Conv_{Gain}$  is the conversion gain of the ED,  $v_{in}$  is the input signal amplitude, and  $k_{ED}$  is the ED scaling factor (in units of 1/V). Combining (4), (5), and (7), the  $k_{ED}$  of the designed ED in the signal passband is given as

$$k_{\rm ED} = (g_{\rm m2} + g_{\rm mb2}) \cdot Z_{\rm out}$$

$$\simeq [1 + (n-1)^2] \cdot \frac{I_{\rm DS}}{2(nV_{\rm T})^2} \cdot R_{\rm FB}$$

(9)

which is only dependent on design parameters.

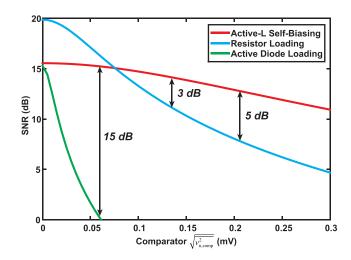

To compare the two conventional biasing schemes with the proposed active-L biasing scheme, the SNR at the ED output was calculated. Assuming that all three biasing schemes use the same DTMOS configuration as the input stage, the SNR can be written as

$$SNR = \frac{(g_{m2} + g_{mb2})^2 \cdot \frac{v_{in}^4}{4} \cdot R_{out}^2}{i_{n,ED}^2 \cdot R_{out}^2 + v_{n,comp}^2}$$

(10)

where  $i_{n,ED}^2$  is the total integrated noise current of the ED input transistor,  $R_{\text{out}}$  is the output resistance in the passband, and  $\overline{v_{n,\text{comp}}^2}$  is the total input-referred noise of the comparator. It can be shown that if the ED loading and comparator are noiseless, the SNR is independent of  $R_{\text{out}}$  and all the biasing schemes would have the same SNR. However, if  $\overline{v_{n,\text{comp}}^2}$  is significant compared to the ED noise, higher  $R_{\text{out}}$ , and therefore, higher  $k_{\text{ED}}$  lead to better SNR. Simulation with an ED current of 5 nA and a 3.2-mV input signal for these three bias schemes is depicted in Fig. 7. When the comparator noise is large, the active-L self-biased scheme achieves the highest SNR.

Fig. 8. (a) Schematic of the dynamic two-stage comparator. (b) Simulation showing first and second stage output voltages.

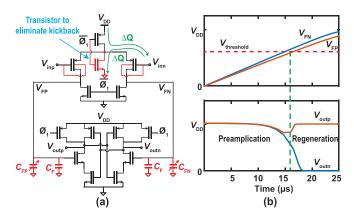

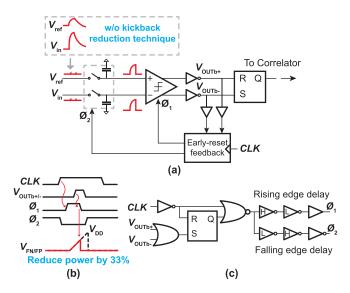

# C. Comparator and S/H Stage

The output of the ED is digitized by a comparator, which serves as a 1-bit quantizer. Due to the  $2\times$  oversampling, the comparator operates at 600 Hz. The comparator is implemented with a  $g_m C$  integrator as a preamplifier followed by a regenerative latch [19]. The operation is as follows: 1) once  $\overline{\phi}$  goes low, a current determined by the inputs is integrated on  $C_F$  until 2) the voltage crosses the latch threshold voltage,  $V_{\text{threshold}}$ , after which the positive feedback latch regenerates producing complementary rail-to-rail outputs. The two-stage dynamic comparator is then reset by the other phase of the clock and ready for the next cycle.

The preamplifier is typically designed with a moderate integration gain of  $\sim$ 5 V/V to suppress the latch input-referred noise. Therefore, the preamplifier usually dominates the noise performance of the entire comparator. As can be observed in [19], adding matched capacitance at the preamplifier output prolongs the integration time and limits the preamplifier noise bandwidth, which effectively reduces the comparator noise. In this design, a 480-fF metal-insulator-metal (MIM) capacitor was used and placed in a common centroid layout to ensure good matching. Compared with the same comparator without explicitly loading the preamplifier, the noise power is reduced by  $8\times$ , while the power consumption increases by only  $5\times$  in simulation because of the  $C_F V_{\rm DD}^2$  energy. Since the comparator is operating at a low speed and the dynamic power of the preamplifier is minimal, loading the preamplifier results in a good noise versus power tradeoff. Moreover, as shown in Fig. 8(a), the input pair also uses a DTMOS configuration, which increases the transconductance resulting in a lower input-referred noise at no power cost. Simulation showed that the effective transconductance increased by 51% and the noise power reduced by 66%. With the help of the preamplifier loading and increased transconductance, the simulated comparator noise was suppressed from 505 to 104  $\mu$ V<sub>RMS</sub>.

The comparison threshold voltage is tuned with a dual 5-bit binary weighted capacitor DAC (CDAC) in parallel with  $C_F$ . By changing the load capacitance, the comparator offset voltage changes accordingly. Assuming the capacitance difference between the two outputs ( $\Delta C_F$ ) is much less

Fig. 9. (a) Schematic of the comparator, S/H stage, and clocking. (b) Timing diagram of the early reset feedback. (c) Schematic of the early reset feedback.

than  $C_{\rm F}$ , the comparison threshold voltage can be written as

$$v_{\rm os,DAC} = \frac{\Delta C_{\rm F}}{C_{\rm F}} \cdot n \cdot V_{\rm T}. \tag{11}$$

Thus, the threshold voltage increases linearly with  $\Delta C_{\rm F}$ , and is constant after the CDAC is configured. The CDAC uses metal-oxide-metal (MOM) capacitors with a unit capacitance of 3.7 fF ( $C_{\rm F}=0.65$  pF), corresponding to  $\sim\!200$ - $\mu\rm V$  resolution. A reference ladder provides a voltage reference to the negative terminal of the comparator. The reference ladder contains 64 diode-connected PMOS transistors in series. A 5-bit MUX selects the output node as the reference voltage, providing a tuning step size of 6.25 mV and a range of 200 mV.

The biggest challenge with this dynamic architecture is the comparator kickback via  $C_{\rm gs}$ ,  $C_{\rm bs}$ ,  $C_{\rm gd}$ , and  $C_{\rm bd}$ . Due to the unbalanced output impedances of the ED ( $\sim 100~{\rm M}\Omega||1.7~{\rm pF}$ ) and the reference ladder ( $\sim 2~{\rm G}\Omega||50~{\rm pF}$ ), the kickback charge introduces unequal voltage perturbations. This voltage difference would lead to a comparison error in subsequent cycles since the time constant at both nodes is much larger than one clock period. To eliminate this error, two techniques were implemented.

- An additional reset transistor was placed at the source of the input pair, which ensures that V<sub>gs</sub> always resets to V<sub>DD</sub>, such that the same amount of charge is injected into the input when φ is asserted high and is removed when φ is deasserted (Fig. 8). This results in zero net kickback charge into the ED and reference ladder during each cycle, preventing incomplete settling.

- 2) A S/H stage was added in front of the comparator that provides matched impedances for both inputs and temporarily stores the kickback charge. The sampling capacitor is 1.9 pF, much larger than the parasitic capacitance of the input transistor. Therefore, the only kickback effect is a ~2-mV common-mode spike at the comparator input, which does not lead to a comparison error. The sampling capacitor and the ED output capacitance limit the baseband bandwidth to 300 Hz.

Fig. 10. Digital correlator baseband logic with wake-up signal output driver.

Fig. 11. (a) Simulated switching threshold for an inverter with minimum width and length across different corners and supply voltages. (b) Simulated normalized leakage current of the designed inverter across corners.

An early reset feedback was implemented to generate a two phase non-overlapping clock efficiently and save comparator dynamic power simultaneously. As illustrated in Fig. 9, the comparator resets once the comparator output is latched, such that the dynamic power of the integrator is reduced from  $2fC_FV_{DD}^2$  to  $2fC_FV_{threshold}^2$ . Since a large capacitance  $C_{\rm F}$  is added, the power savings are significant. Simulation shows that 33% of total comparator power is saved when the WuRX RF input power is -69 dBm, or 0.7 mV at the comparator input. The early reset feedback was implemented as shown in Fig. 9(c), where an SR-latch captures the rising edge of either  $V_{\text{outb+}}$  or  $V_{\text{outb-}}$  and asserts CLK to "low" to turn off the integration. The non-overlapping phases are generated with two inverter chains: one creates a pos-edge delay and the other creates a neg-edge delay. The pos-edge delay was created by four cascaded inverters, where the first was designed to be a high-skewed inverter followed by a low-skewed inverter with  $W_P/W_N$  of 6 and 0.5, respectively. Similarly, the neg-edge delay was created by flipping the order of the skewed inverters. Compared with a conventional twophase clock generator where cascaded latches are used, this method has lower power consumption with a 0.4-V supply.

Fig. 12. Schematic of the relaxation oscillator.

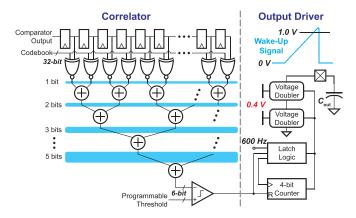

## D. Digital Baseband

Fig. 10 shows the digital baseband correlation logic that processes the incoming data from the comparator. With the lack of a power hungry PLL for synchronization, the correlator provides an energy efficient way to overcome phase asynchronization by operating at a  $2\times$  oversampling rate to sample the incoming bits [20]. An optimal 16-bit code sequence (1110101101100010) was designed such that it has both a large Hamming distance from all of its shifted versions (D=9) and from the all-0 sequence (D=9). A family of codes also exists, but with slightly lower Hamming distances (D < 8). As the input sequence shifts along the D flip-flop chain, the correlator computes the Hamming distance between the sequence and the programmable 32-bit oversampled code book. Once the value is below a preset threshold, the pattern is declared detected and the correlator generates a wake-up signal. To drive the main receiver with a higher supply voltage, the output driver was designed to generate a > 1-V signal with 5 ms duration assuming a 10-pF load. When the correlator sends a wake-up signal to the driver, it resets a 4-bit counter and the signal is latched to leave the cascode voltage doubler enabled until the counter rolls over. The charge pump and counter make the wake-up signal look like a ramp. Also, to use the same 0.4-V supply, the digital baseband operates in the sub- $V_t$  region implemented with a custom designed logic gate library using thick oxide devices. All the gates were designed using only inverters and transmission gates for the highest robustness in subthreshold [21].

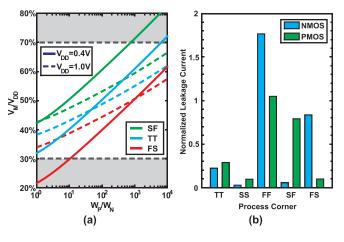

From a static performance perspective, digital logic gates operating in the sub- $V_{\rm t}$  region need extra attention to the transistor sizing to overcome process variation. To see this, the inverting threshold  $V_{\rm M}$  of an inverter with minimum width and length NMOS was simulated across the width of the PMOS at different process corners [Fig. 11(a)], where the solid and dashed lines correspond to a 0.4- and 1.0-V supply voltage, respectively. For an ideal inverter with a negligible transition region, the noise margin is equal to the lower value of either  $V_{\rm M}$  or  $V_{\rm DD}-V_{\rm M}$ . It can be seen that the inverter maintains larger than 30%  $V_{\rm DD}$  noise margin when operating above- $V_{\rm t}$  across all corners, while it fails when operating in the sub- $V_{\rm t}$  region without proper sizing. Another important design

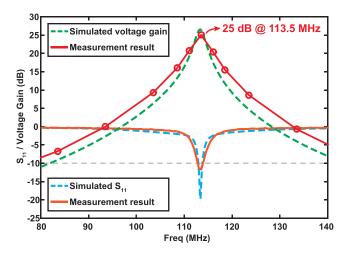

Fig. 13. Simulated and measured transformer  $S_{11}$  and voltage gain.

consideration comes from the power dissipation. For a digital circuit, it is well known that the power consumption can be written as

$$P_{\text{tot}} = P_{\text{leak}} + P_{\text{dyn}} = V_{\text{DD}}I_{\text{leak}} + \alpha C_{\text{L}}V_{\text{DD}}^2 f \qquad (12)$$

where  $I_{\text{leak}}$  is the average leakage current,  $\alpha$  is the activity factor,  $C_{\text{L}}$  is the load capacitor, and f is the clock rate.

In addition to the low clock rate, since ideally the correlator only computes when the signal pattern changes,  $\alpha$  is nearly zero, both of which make the leakage power dominant and thus the design target here. To equate the NMOS and PMOS leakages in this process where the PMOS has lower mobility and  $V_t$  is 90 mV higher than an NMOS in the typical-typical (TT) corner,  $5 \times$  NMOS devices were stacked. Moreover, the PMOS was re-sized to  $1.6 \times$  larger width to achieve 30%  $V_{\rm DD}$  noise margin even in the worst case fast-slow (FS) corner. Fig. 11(b) shows the leakage current of the designed inverter across corners, which is normalized to the leakage current of a minimum size inverter at TT. The normalized  $I_{\rm leak}$  is 0.26 in the TT corner and 1.41 in the fast-fast (FF) corner.

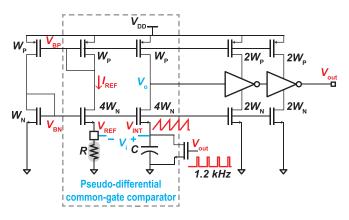

# E. Relaxation Oscillator

The system clock for the comparator, digital baseband, and charge pump is generated from a relaxation oscillator. As shown in Fig. 12, the oscillator is composed of a reference generator, where one branch is shared with a pseudodifferential common-gate comparator, an inverter chain, and a reset switch. The reference generator with all four transistors operating in the sub- $V_t$  region, generates a reference current  $I_{\text{REF}}$  and a reference voltage  $V_{\text{REF}}$  through an off-chip resistor.  $I_{REF}$  is used to charge a MIM capacitor that is connected to a common-gate comparator (shown in the dashed box). The comparator output is pulled high after  $V_{\text{INT}}$  exceeds  $V_{\rm REF}$ . Then, the inverter chain is triggered to close the reset switch and reset the integration capacitor. The capacitor is charged and discharged periodically with a period of  $\sim RC$ . The clock buffer was implemented with current-starved inverters whose delay are determined by  $I_{REF}$ , which has better

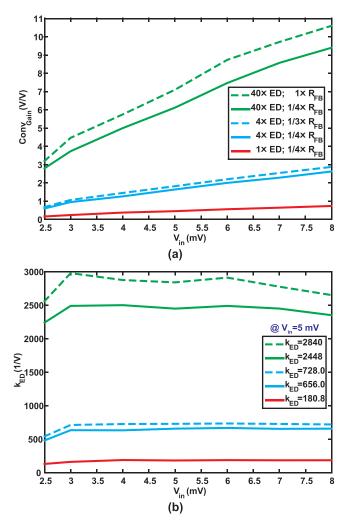

Fig. 14. Measurement results. (a) ED conversion gain. (b) Scaling factor  $k_{\rm ED}$ .

energy efficiency than dynamic inverters  $(CV_{DD}^2)$ . Since the power consumption is largely determined by the static power of the reference generator and comparator, the oscillator power consumption can be minimized by using a large bias resistor. The resistor was chosen to be 30 M $\Omega$  and  $I_{REF}$  to be  $\sim 0.5$  nA. To compensate the variation of the capacitor value and comparator delay, the off-chip resistor is tuned to adjust the oscillation frequency to 1.2 kHz. The oscillator output is divided and buffered to a 600-Hz system clock with 50% duty cycle. The frequency varies from 617 to 585 Hz, when the supply voltage changes from 0.35 to 0.45 V. This corresponds to 5.3% frequency change when the supply changes by 25%. When the temperature changes by 10 °C, the frequency changes by 4.9%. The supply and temperature sensitivity are mainly caused by the comparator and buffer delay. The  $2\times$ oversampling scheme and short data sequence (53.3 ms) make the system insensitive to clock mismatch. Based on systemlevel Monte Carlo simulations where the clock mismatch is modeled as normal distribution with 1.5% standard deviation (i.e., 99.7% samples are within  $\pm 4.5\%$  clock mismatch), the sensitivity deviation is less than 0.5 dB.

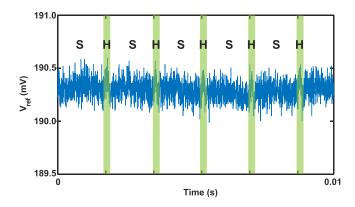

Fig. 15. Measured reference ladder output voltage with sample and hold phases annotated.

# IV. MEASUREMENT RESULTS

To characterize the passive voltage gain from the transformer/filter, a conventional two-port measurement such as  $S_{21}$  using a vector network analyzer (VNA) is not possible due to the high (i.e., non-50  $\Omega$ ) output impedance. Instead, we first characterized the ED by connecting a 50- $\Omega$  load at the input without the transformer to provide matching and measured the output voltage after applying a known input signal. We then replaced the 50- $\Omega$  resistor with the transformer and again measured the output voltage. The transformer gain was then calculated using

$$A_{\rm V} = \frac{V_{\rm in,1}}{V_{\rm in,2}} \cdot \sqrt{\frac{V_{\rm out-ED,2}}{V_{\rm out-ED,1}}}.$$

(13)

Using the above-mentioned procedure,  $A_{\rm V}=25$  dB was measured, which is in agreement with simulation results (Fig. 13).  $S_{11}$  measurements show excellent matching at the signal frequency (113.5 MHz), and is also in agreement with simulations.

The measured conversion gain,  $Conv_{Gain}$ , and scaling factor,  $k_{ED}$ , versus  $V_{in-ED,1}$  for different ED bias current settings are shown in Fig. 14. While the  $Conv_{Gain}$  is proportional to  $V_{in-ED,1}$  as shown in Fig. 14(a), Fig. 14(b) shows that  $k_{ED}$  is independent of  $V_{in-ED,1}$ , which is expected from (8) and (9). When the ED is configured for 2 nW (i.e.,  $1 \times ED$ ) with four parallel feedback units (i.e.,  $1/4 \times R_{FB,unit}$ ) to achieve a 300-Hz low-pass corner,  $k_{ED} = 180.8$  (1/V). Using  $1/3 \times R_{FB,unit}$  and  $4 \times ED$ , the ED achieves  $k_{ED} = 728$  (1/V), which is  $\sim 4 \times$  larger than the  $1 \times ED$  configuration, as expected. At higher powers (e.g.,  $40 \times ED$ ),  $r_0$  dominates, and thus the improvement in  $k_{ED}$  saturates.

The comparator noise was measured by sweeping the input differential voltage and fitting the resulting distribution. Since the comparator noise is mostly white, fitting with a Gaussian distribution allows the noise and offset to be extracted. Nine chips were measured with the input-referred noise varying from 89 to 95  $\mu V_{\rm RMS}$ , slightly lower than the simulated value at the TT corner, likely due to process variation. The measured offset varied from 0.69 to 1.16 mV, which is easily covered by the 5-bit tuning range of the comparator CDAC.

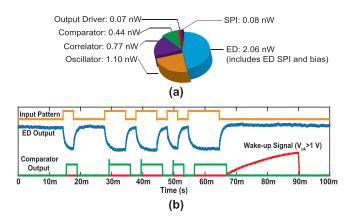

Fig. 16. (a) System power breakdown pie chart. (b) Transient waveforms at each node.

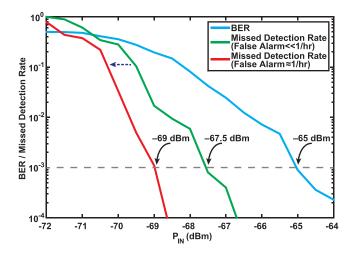

Fig. 17. BER and MDR waterfall curves with a 300-bps data rate.

The performance of the kickback reduction technique was validated by measuring the output voltage of the reference ladder, which connects to one of the comparator inputs, with the transmitted signal at the other input. Since this is a very high impedance node ( $\sim$ 2 G $\Omega$ ||50 pF), a unity-gain buffer with low input bias current was used to buffer the voltage. The measured data are shown in Fig. 15, where the sample (S) and hold (H) phases are annotated. Only small spikes appear during the H phase that are due to the leakage of the sampling switch since the switch OFF-resistance is not significantly larger than the reference ladder impedance. The spikes always settle before the beginning of the next cycle owing to the zero net charge kickback, and as such do not affect the following comparisons.

Fig. 16(a) shows the measured power breakdown of the WuRX. The total power consumption is 4.5 nW when the ED is set to 2.0 nW. Transient waveforms shown in Fig. 16(b) demonstrate correct detection when the correct code is transmitted.

Fig. 17 shows the waterfall curves for conventional bit error rate (BER) measured at the comparator output, and the wake-up signal missed detection rate (MDR) measured after the digital baseband (BB) logic. The BER was measured

|                                     | [4]<br>JSSC'09             | [22]<br>ISSCC'10          | [3]<br>ISSCC'11      | [7]<br>CICC'13        | [6]<br>JSSC'16                                                            | [9]<br>ISSCC'16   |                    | This Work                          |

|-------------------------------------|----------------------------|---------------------------|----------------------|-----------------------|---------------------------------------------------------------------------|-------------------|--------------------|------------------------------------|

| Technology                          | 90 nm                      | 90 nm                     | 130 nm               | 130 nm                | 65 nm                                                                     | 65 nm             |                    | 180 nm                             |

| Carrier Frequency                   | 2 GHz                      | 915 MHz                   | 402 MHz              | 403 MHz               | 2.4 GHz                                                                   | 2.4 GHz           |                    | 113.5 MHz                          |

| Modulation                          | ООК                        | ООК                       | FSK                  | оок                   | ООК                                                                       | OOK               |                    | оок                                |

| Supply Voltage                      | 0.5 V                      | 1 V                       | 1 V                  | 1.2/0.5 V             | 0.5 V                                                                     | 1/0.5 V           |                    | 0.4 V                              |

| Digital Correlator                  | No                         | No                        | No                   | 31-bit                | No                                                                        | 31-bit            |                    | 32-bit <sup>1</sup>                |

| <b>External Components</b>          | BAW filter                 | L for MN<br>+ LNA loading | XTAL<br>+ LC MN      | XTAL<br>+ LC MN       | $\begin{array}{c} \operatorname{BGA} \\ \operatorname{SMD} L \end{array}$ | XTAL + MN         |                    | Transformer/filter                 |

| Oscillator                          | Ring osc.                  | No                        | Inj-locked osc.      | XTAL osc.             | LC DCO                                                                    | XTAL osc.         |                    | Relaxation osc.                    |

| Gain Stage(s)                       | ${ m IF}^2$                | RF/BB <sup>2</sup>        | ${ m IF}^2$          | $ED^2$                | IF/BB <sup>2</sup>                                                        | $ED^2$            | ED/BB <sup>2</sup> | TF/ED/BB                           |

| Interferer Rejection                | BAW filter                 | LC MN<br>+ LNA loading    | LC MN<br>+ IF filter | LC MN<br>+ correlator | LC MN<br>+ N-path filters                                                 | Digital processor |                    | Transformer/filter<br>+ correlator |

| SIR (dB) @ $ \Delta f $             | > -5 @ 10 MHz <sup>3</sup> | N/A                       | N/A                  | +3.3<br>N/A           | -31/-27<br>@ 5 MHz <sup>3</sup>                                           | N/A               |                    | -15<br>@ 5 MHz <sup>4</sup>        |

| Data Rate                           | 100 kbps                   | 10 kbps                   | 200 kbps             | 12.5 kbps             | 10 kbps                                                                   | 8.192 kbps        |                    | 0.3 kbps                           |

| Energy/bit                          | 520 pJ                     | 5100 pJ                   | 220 pJ               | 9.3 pJ                | 9900 pJ                                                                   | 12.7 pJ           | 28.8 pJ            | 15.0 pJ                            |

| Sensitivity                         | -72 dBm                    | -80 dBm                   | -70 dBm              | -45.5 dBm             | -97 dBm                                                                   | -39 dBm           | -56.5 dBm          | -69 dBm <sup>5</sup>               |

| Normalized Sensitivity <sup>6</sup> | -97 dB                     | -100 dB                   | -123 dB              | -66 dB                | -137 dB                                                                   | -58.6 dB          | -76.1 dB           | -81.4 dB                           |

| Power                               | 52 μW                      | 51 μW                     | 44 μW                | 116 nW                | 99 μW                                                                     | 104 nW            | 236 nW             | 4.5 nW                             |

$TABLE\ I$   $Comparison\ With\ Previously\ Published\ State-of-the-Art\ WuRXs$

<sup>&</sup>lt;sup>6</sup> Calculated by normalizing the sensitivity to data rate using either (16) or (17) depending on demodulation method.

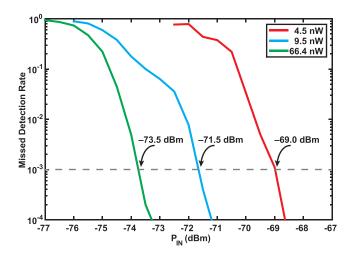

Fig. 18. MDR waterfall curves for different power settings with a 300-bps data rate.

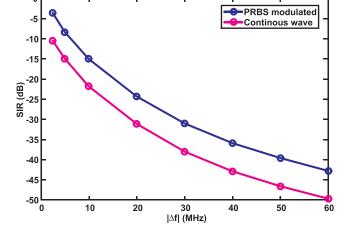

Fig. 19. SIR curve versus interferer frequency offset  $|\Delta f|$  to carrier frequency for a worst case 300-bps PRBS-modulated jammer and a CW jammer.

under the assumption of perfect synchronization between clock and input data, while the MDR was measured with random (i.e., not synchronized) transmission. To achieve a BER =  $10^{-3}$ , the input signal power  $P_{\rm IN} = -65$  dBm. With the same comparator and correlator threshold,  $P_{\rm IN} = -67.5$  dBm for MDR =  $10^{-3}$  with a false alarm rate of  $\ll$  1/hr. By adjusting the comparator threshold,  $P_{\rm IN} = -69$  dBm was achieved for MDR =  $10^{-3}$  with a false alarm rate of  $\approx$  1/hr, which is where

the sensitivity  $P_{\rm SEN}$  is defined, and 4-dB coding gain is shown compared to the BER measurement. MDR measurements were also taken at higher power ED settings (Fig. 18). For the 4× ED case,  $P_{\rm SEN} = -71.5$  dBm and the power consumption is 9.5 nW. For the  $40\times$  ED case,  $P_{\rm SEN} = -73.5$  dBm and the power consumption is 66.4 nW.

A modulated signal tone along with a pseudorandom binary sequence (PRBS) modulated or continuous wave (CW) jam-

$<sup>^1</sup>$  16-bit code sequence with 2 imes oversampling.  $^2$  The front-end matching network also has modest passive gain.

<sup>&</sup>lt;sup>3</sup> Measured using CW jammer with signal input power for BER=  $10^{-3} + 3$  dB.

<sup>&</sup>lt;sup>4</sup> Measured using CW jammer with signal input power for BER=  $10^{-3} + 1$  dB.

$<sup>^{5}</sup>$  Defined with less than  $10^{-3}$  missed detection rate.

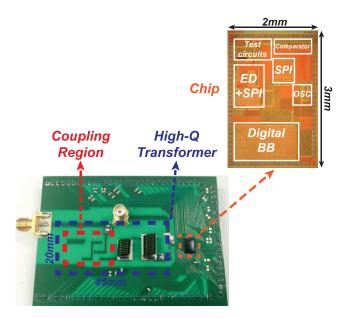

Fig. 20. Top: picture of annotated die micrograph. Bottom: whole WuRX.

mer at frequency offset  $\Delta f$  to the signal center frequency were used to test WuRX performance under interference. The input signal power was set to 1 dB higher than the power where BER =  $10^{-3}$  (i.e., at -64 dBm), and the interferer power at  $\Delta f$  was swept until BER =  $10^{-3}$ . The signal-to-interferer ratio (SIR) versus  $|\Delta f|$  is depicted in Fig. 19. Because of the high-Q nature of the transformer/filter, for PRBS jammer a SIR < -30 dB was achieved at  $|\Delta f| = 30$  MHz. At the chosen FM band, since a narrowband FM signal would look like a CW jammer and only causes a dc tone at the ED output, an additional 7 dB rejection compared to a PRBS jammer was achieved. Moreover, a CW jammer is unlikely to cause a false alarm due to the correlator. Therefore, by designing a longer bit correlator, the code space can be increased, which not only improves interferer resilience further in terms of false alarms, but also enables more WuRXs with different wake-up codes in the sensor network. The die micrograph along with the whole system photograph is shown in Fig. 20.

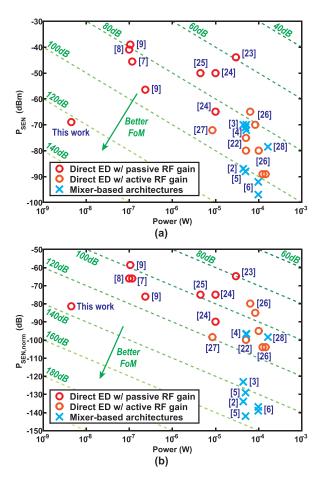

# V. FIGURE OF MERIT AND COMPARISON

As discussed in Section I, for WuRXs used in low-average throughput applications, power consumption and sensitivity are the most important metrics, and thus the following FoM is defined:

$$FoM_{LAT}(dB) = -P_{SEN} - 10\log\frac{P_{dc}}{1 \text{ mW}}$$

(14)

where  $P_{\rm SEN}$  is the sensitivity in dBm and  $P_{\rm dc}$  is the power consumption. For high-average throughput applications, data rate is important. Therefore, the following FoM is used:

$$FoM_{HAT}(dB) = -P_{SEN,norm} - 10\log\frac{P_{dc}}{1 \text{ mW}}$$

(15)

Fig. 21. (a) Sensitivity versus power (FoM  $_{LAT}$  ). (b) Sensitivity normalized to data rate versus power (FoM  $_{HAT}$  ).

where  $P_{\text{SEN,norm}}$  is the sensitivity normalized to data rate and calculated using one of the following equations:

$$P_{\text{SEN,norm}}(dB) = P_{\text{SEN}} - 5\log BW_{\text{BB}} \tag{16}$$

$$P_{\text{SEN,norm}}(dB) = P_{\text{SEN}} - 10\log BW_{\text{BB}}$$

(17)

where  $5 \log BW_{BB}$  in (16) is used for designs with a non-linear squaring function for envelope detection [4], [7]–[10], [12], [22]–[28], and  $10 \log BW_{BB}$  in (17) is used for designs with a linear operation to demodulate the signal [3], [6] or designs using a non-linear squaring function for envelope detection after high active pre-ED gain with sharp filtering [2], [5] (i.e., where convolution noise dominates [12]). A survey of prior-art WuRXs is shown in Fig. 21 for both FoMs. The low baseband bandwidth and high passive RF gain afforded by the high input impedance ED and FM-band high-Q passives enabled the proposed design to achieve an  $FoM_{LAT} = 122.5$  dB, which is over an order of magnitude higher than prior work. For highaverage throughput applications where data rate is important, while this design achieved the best  $FoM_{HAT} = 134.9 \text{ dB}$ among the direct ED architectures, mixer-based architectures achieved comparable, and in some cases better, FoM<sub>HAT</sub> at the expense of four decades higher power consumption. Table I summarizes the measurement results of the proposed WuRX and compares the results to the state-of-the-art WuRXs.

## VI. CONCLUSION

In this paper, a 0.4-V 113.5-MHz OOK-modulated WuRX that achieves -69-dBm sensitivity consuming only 4.5 nW in a 0.18-μm SOI CMOS process is presented. The WuRX was designed for emerging event-driven low-average throughput applications to reduce system power. While conventional direct envelope detection architectures can achieve low power at moderate sensitivities, this design breaks the conventional tradeoff to achieve ultralow power with high sensitivity by: 1) reducing the baseband signal bandwidth to 300 Hz; 2) modulating OOK signal with a custom 16-bit code sequence to get 4-dB coding gain; 3) employing an off-chip high-Q transformer/filter with 25-dB passive voltage gain enabled by an ED with high input impedance; 4) achieving higher conversion gain using an active-L-biased ED; 5) digitizing the ED output via a regenerative comparator with kickback elimination; and 6) decoding the received OOK signal using a high-V<sub>t</sub> subthreshold digital baseband correlator, operating with 2× oversampling to overcome phase asynchronization, where the clock is generated by a 1.1-nW relaxation oscillator.

### REFERENCES

- P. P. Mercier and A. P. Chandrakasan, *Ultra-Low-Power Short-Range Radios*. New York, NY, USA: Springer, 2015.

- [2] T. Abe et al., "An ultra-low-power 2-step wake-up receiver for IEEE 802.15.4g wireless sensor networks," in *IEEE Symp. VLSI Circuits Dig.*, Jun. 2014, pp. 1–2.

- [3] J. Pandey, J. Shi, and B. Otis, "A 120 μW MICS/ISM-band FSK receiver with a 44 μW low-power mode based on injection-locking and 9x frequency multiplication," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2011, pp. 460–462.

- [4] Ñ. M. Pletcher, S. Gambini, and J. Rabaey, "A 52 μW wake-up receiver with -72 dBm sensitivity using an uncertain-IF architecture," *IEEE J. Solid-State Circuits*, vol. 44, no. 1, pp. 269–280, Jan. 2009.

- [5] C. Bryant and H. Sjöland, "A 2.45 GHz, 50 μW wake-up receiver frontend with –88 dBm sensitivity and 250 kbps data rate," in *Proc. IEEE Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2014, pp. 235–238.

- [6] C. Salazar, A. Cathelin, A. Kaiser, and J. Rabaey, "A 2.4 GHz interfererresilient wake-up receiver using a dual-IF multi-stage N-path architecture," *IEEE J. Solid-State Circuits*, vol. 51, no. 9, pp. 2091–2105, Sep. 2016.

- [7] O. Seunghyun, N. Roberts, and D. Wentzloff, "A 116 nW multi-band wake-up receiver with 31-bit correlator and interference rejection," in Proc. IEEE Custom Integr. Circuits Conf., Apr. 2013, pp. 1–4,

- [8] N. E. Roberts and D. D. Wentzloff, "A 98 nW wake-up radio for wireless body area networks," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Montreal, QC, Canada, Jun. 2012, pp. 373–376.

- [9] N. E. Roberts et al., "A 236 nW -56.5 dBm-sensitivity bluetooth low-energy wakeup receiver with energy harvesting in 65 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2016, pp. 450-451.

- [10] H. Jiang et al., "A 4.5 nW wake-up radio with -69 dBm sensitivity," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 416-417.

- [11] P. M. Nadeau, A. Paidimarri, P. P. Mercier, and A. P. Chandrakasan, "Multi-channel 180 pJ/b 2.4 GHz FBAR-based receiver," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2012, pp. 381–384.

- [12] X. Huang, G. Dolmans, H. de Groot, and J. R. Long, "Noise and sensitivity in RF envelope detection receivers," *IEEE Trans. Circuits* Syst. II, Exp. Briefs, vol. 60, no. 10, pp. 637–641, Oct. 2013.

- [13] K. Entesari and G. M. Rebeiz, "A differential 4-bit 6.5-10-GHz RF MEMS tunable filter," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 3, pp. 1103–1110, Mar. 2005.

- [14] Coilcraft, Inc., Cary, IL, USA. (Oct. 2015). Square Air Core Inductors 1515SQ 2222SQ 2929SQ. [Online]. Available: http://www.coilcraft.com/ pdfs/1515sq.pdf

- [15] J.-S. Hong, Microstrip Filters for RF/Microwave Applications, 2nd ed. Hoboken, NJ, USA: Wiley, 2011.

- [16] M. Seok, G. Kim, D. Blaauw, and D. Sylvester, "A portable 2-transistor picowatt temperature-compensated voltage reference operating at 0.5 V," *IEEE J. Solid-State Circuits*, vol. 47, no. 10, pp. 2534–2545, Oct. 2012.

- [17] F. Assaderaghi, D. Sinitsky, S. A. Parke, J. Bokor, P. K. Ko, and C. Hu, "Dynamic threshold-voltage MOSFET (DTMOS) for ultra-low voltage VLSI," *IEEE Trans. Electron Devices*, vol. 44, no. 3, pp. 414–422, Mar. 1997.

- [18] S. Bandyopadhyay, P. P. Mercier, A. C. Lysaght, K. M. Stankovic, and A. P. Chandrakasan, "A 1.1 nW energy-harvesting system with 544 pW quiescent power for next-generation implants," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2812–2824, Dec. 2014.

- [19] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. A. M. Klumperink, and B. Nauta, "A 10-bit charge-redistribution ADC consuming 1.9 μW at 1 MS/s," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 1007–1015, May 2010.

- [20] P. P. Mercier and A. P. Chandrakasan, "A supply-rail-coupled eTextiles transceiver for body-area networks," *IEEE J. Solid-State Circuits*, vol. 46, no. 6, pp. 1284–1295, Jun. 2011.

- [21] A. Wang and A. Chandrakasan, "A 180-mV subthreshold FFT processor using a minimum energy design methodology," *IEEE J. Solid-State Circuits*, vol. 40, no. 1, pp. 310–319, Jan. 2005.

- [22] X. Huang, S. Rampu, X. Wang, G. Dolmans, and H. de Groot, "A 2.4 GHz/915 MHz 51 μW wake-up receiver with offset and noise suppression," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2010, pp. 222–224.

- [23] J. Choi, K. Lee, S.-O. Yun, S.-G. Lee, and J. Ko, "An interference-aware 5.8 GHz wake-up radio for ETCS," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2012, pp. 446–447.

- [24] K.-W. Cheng, X. Liu, and M. Je, "A 2.4/5.8 GHz 10 μW wake-up receiver with -65/-50 dBm sensitivity using direct active RF detection," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2012, pp. 337–340.

- pp. 337–340.

[25] S.-E. Chen, C.-L. Yang, and K.-W. Cheng, "A 4.5 μW 2.4 GHz wake-up receiver based on complementary current-reuse RF detector," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2015, pp. 1214–1217.

- [26] X. Huang, P. Harpe, G. Dolmans, and H. de Groot, "A 915MHz ultralow power wake-up receiver with scalable performance and power consumption," in *Proc. IEEE Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2011, pp. 543–546.

- [27] D.-Y. Yoon et al., "A new approach to low-power and low-latency wake-up receiver system for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 47, no. 10, pp. 2405–2419, Oct. 2012.

- [28] S. Moazzeni, M. Sawan, and G. E. R. Cowan, "An ultra-low-power energy-efficient dual-mode wake-up receiver," *IEEE Trans. Circuits* Syst. I, Reg. Papers, vol. 62, no. 2, pp. 517–526, Feb. 2015.

**Po-Han Peter Wang** (S'16) received the B.S. degree in electrical engineering from National Taiwan University (NTU), Taipei, Taiwan, in 2011, and the M.S. degree in electrical and computer engineering from the University of California at San Diego (UCSD), La Jolla, CA, USA, in 2014, where he is currently pursuing the Ph.D. degree.

He was an RFIC Design Intern with Broadcom Corporation, San Diego, CA, USA, in 2013. His current research interests include the design of energyefficient transceiver for wireless communications,

reconfigurable RF front-ends and filters, and ultra-low-power mixed-signal circuits.

Haowei Jiang (S'15) received the B.S. degree in electrical engineering from the Huazhong University of Science and Technology, Wuhan, China, in 2014, and the M.S. degree in electrical and computer engineering from the University of California at San Diego, La Jolla, CA, USA, in 2016, where he is currently pursuing the Ph.D. degree.

His current research interests include low-power integrated analog/mixed-signal circuit design for sensing systems and biomedical devices.

Li Gao (S'14) received the B.S. and M.S. degrees in electronic engineering from the South China University of Technology, Guangzhou, China, in 2012 and 2015, respectively. He is currently pursuing the Ph.D. degree in electrical and computer engineering with the University of California at San Diego, La Jolla, CA, USA.

His current research interests include RF circuits and antennas.

Pinar Sen (S'13) received the B.S. and M.S. degrees in electrical and electronics engineering from Middle East Technical University, Ankara, Turkey, in 2011 and 2014, respectively. She is currently pursuing the Ph.D. degree in electrical and computer engineering with the University of California at San Diego, La Jolla, CA, USA.

Her current research interests include coding and information theory in multi-user networks, with applications in wireless communication.

South Korea, in 1996, and the M.S. degrees in electrical engineering and in statistics and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, USA, in 2001, 2006, and 2006, respectively.

In 2006, he joined the University of California at San Diego, La Jolla, CA USA, where he is currently a Professor with the Department of Electrical and

Computer Engineering. He has co-authored the book Network Information Theory (Cambridge University Press, 2011). His current research interests include information theory, communication engineering, and data science.

Dr. Kim was a recipient of the 2008 NSF Faculty Early Career Development Award, the 2009 US-Israel Binational Science Foundation Bergmann Memorial Award, the 2012 IEEE Information Theory Paper Award, and the 2015 IEEE Information Theory Society James L. Massey Research and Teaching Award for Young Scholars. He served as an Associate Editor of the IEEE TRANSACTIONS ON INFORMATION THEORY and a Distinguished Lecturer for the IEEE Information Theory Society.

**Gabriel M. Rebeiz** (S'86–M'88–SM'93–F'97) received the Ph.D. degree from the California Institute of Technology, Pasadena, CA, USA.

From 1988 to 2004, he was with the University of Michigan, Ann Arbor, MI, USA. His group has optimized the dielectric-lens antenna, which is the most widely used antenna at millimeter-wave and terahertz frequencies. His group also developed several 8- and 16-element phased arrays covering 6-110 GHz on a single silicon chip, the first silicon phased array chip with built-in-self-test capabilities,

the first wafers-scale silicon phased array, and the first millimeter-wave silicon passive imager chip at 85-105 GHz. His group also demonstrated RF microelectro-mechanical systems (MEMS) tunable filters at 1-6 GHz, RF MEMS phase shifters at 1-100 GHz, and high-power high-reliability RF MEMS metal-contact switches. As a consultant, he helped to develop 24- and 77-GHz single-chip SiGe automotive radars, and phased arrays operating at X- to W-bands for defense and commercial applications (SATCOM, automotive, point-to-point communications, and weather radars). Since 2016, he has been elected to the National Academy, where he was involved in phased arrays. He is currently a Distinguished Professor and the Wireless Communications Industry Chair Professor of electrical and computer engineering with the University of California at San Diego (UCSD), La Jolla, CA USA. He also leads a group of 20 Ph.D. students and post-doctoral fellows in the area of millimeter-wave 5G systems and phased arrays, RF-integrated circuits (RFICs), tunable microwaves circuits, and terahertz systems. He has graduated 65 Ph.D. students and 20 post-doctoral fellows. He has authored or coauthored more than 600 IEEE publications and authored the book RF MEMS: Theory, Design and Technology (Wiley, 2003).

Dr. Rebeiz has been an Associate Editor for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES. He has been a Distinguished Lecturer for the IEEE Microwave Theory and Techniques Society (IEEE MTT-S), the IEEE Antennas and Propagation Society (AP-S), and the IEEE Solid-State Circuits Societies. He is a National Science Foundation Presidential Young Investigator. He was a recipient of the URSI Koga Gold Medal, the 2014 IEEE Daniel E. Noble Award for his work on RF MEMS, the 2014 IEEE MTT-S Microwave Prize for his work on phased arrays, the 2012 Intel Semiconductor Technology Council Outstanding Researcher in Microsystems Award, the 2011 IEEE AP-S John D. Kraus Antenna Award, the IEEE MTT-S 2010 Distinguished Educator Award, the 2003 IEEE MTT-S Distinguished Young Engineer Award, the 2000 IEEE MTT-S Microwave Prize for his work on RF MEMS phase shifters, the 1997-1998 Eta Kappa Nu Professor of the Year Award, the 1998 College of Engineering Teaching Award, the 1998 Amoco Teaching Award given to the best undergraduate teacher at the University of Michigan, and the 2008 Teacher of the Year Award of the Jacobs School of Engineering, UCSD. His students have been recipients of a total of 21 Best Paper Awards of the IEEE MTT-S, RFIC, and AP-S conferences.

Patrick P. Mercier (S'04-M'12-SM'17) received the B.Sc. degree in electrical and computer engineering from the University of Alberta, Edmonton, AB, Canada, in 2006, and the S.M. and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 2008 and 2012, respectively.

He is currently an Assistant Professor in electrical and computer engineering with the University of California at San Diego (UCSD), La Jolla, CA, USA, where he is also the Co-Director of the Center

for Wearable Sensors. He has co-edited Ultralow-Power Short Range Radios (Springer, 2015) and Power Management Integrated Circuits (CRC Press, 2016). His current research interests include the design of energy-efficient microsystems, focusing on the design of RF circuits, power converters, and sensor interfaces for miniaturized systems and biomedical applications.

Dr. Mercier was a recipient of the Natural Sciences and Engineering Council of Canada (NSERC) Julie Payette fellowship in 2006, the NSERC Postgraduate Scholarships in 2007 and 2009, an Intel Ph.D. Fellowship in 2009, the 2009 IEEE International Solid-State Circuits Conference (ISSCC) Jack Kilby Award for Outstanding Student Paper at ISSCC 2010, the Graduate Teaching Award in Electrical and Computer Engineering at UCSD in 2013, the Hellman Fellowship Award in 2014, the Beckman Young Investigator Award in 2015, the DARPA Young Faculty Award in 2015, the UCSD Academic Senate Distinguished Teaching Award in 2016, the Biocom Catalyst Award in 2017, and the National Science Foundation CAREER Award in 2018. He has served as an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION from 2015 to 2017. Since 2013, he has been serving as an Associated Editor for the IEEE TRANSACTIONS ON BIOMEDICAL INTEGRATED CIRCUITS, and since 2017, he has been a member of the ISSCC International Technical Program Committee (Technology Directions Sub-Committee), the CICC Technical Program Committee, and an Associate Editor of the IEEE SOLID-STATE CIRCUITS LETTERS.

Drew A. Hall (S'07-M'12) received the B.S. degree (Hons.) in computer engineering from the University of Nevada, Las Vegas, NV, USA, in 2005, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA, in 2008 and 2012, respectively.

From 2011 to 2013, he was a Research Scientist with the Integrated Biosensors Laboratory, Intel Corporation, Santa Clara, CA, USA. Since 2013, he has been an Assistant Professor with the Department of Electrical and Computer Engineering, University of

California at San Diego, La Jolla, CA, USA. His current research interests include bioelectronics, biosensors, analog circuit design, medical electronics, and sensor interfaces.

Dr. Hall was a recipient of the first place in the Inaugural International IEEE Change the World Competition in 2009, the first place in the BME-IDEA invention competition in 2009, the Analog Devices Outstanding Designer Award in 2011, an Undergraduate Teaching Award in 2014, the Hellman Fellowship Award in 2014, and an National Science Foundation CAREER Award in 2015. He is also a Tau Beta Pi Fellow. Since 2015 he has been serving as an Associate Editor for the IEEE TRANSACTIONS ON BIOMEDICAL INTEGRATED CIRCUITS and has been a member of the CICC Technical Program Committee since 2017.